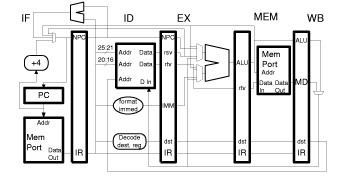

Put the following corrected Problem 3 illustration in Homework 3:

. Also

added this text to Problem 4:

. Also

added this text to Problem 4:To solve this problem first find instructions that set and use the multiple FCC registers in the SPARC V9 Architecture Manual. Then write a program that needs the result of one comparison (say, a<b) several times while also using the result of another (say, c>d). A program not using multiple condition code registers should have to do the comparison multiple times whereas the program you write does each comparison once.)