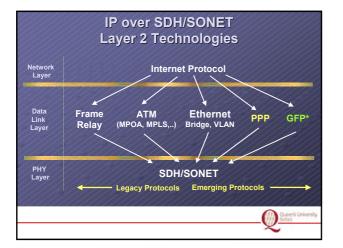

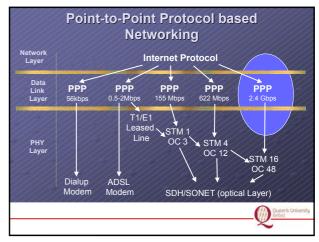

## The Point-to-Point Protocol

- The most efficient layer 2 protocol for encapsulating IP datagrams

- Key applications include ADSL, dialup modems, encapsulated Ethernet, Virtual Local Area Networks (VLAN), Virtual Privet Networks (VPN) etc.

- Key functions:

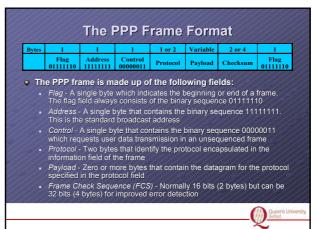

- Framing and Error Control method for encapsulating data over physical layer point-to-point links.

- Link Control Protocol (LCP) functions to establishes, negotiate configure and terminate PPP links between two network nodes.

- Network Control Protocol (NCP) function for upper network protocols, optional for ATM, IP, Ethernet etc.

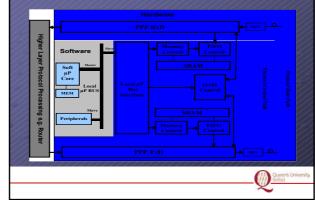

#### Programmable SoPC System Architecture for PPP processing

The Programmable SoPC Architecture for PPP processing is composed of three architectural independent units.

#### This includes :

- Protocol Data-Path Unit

A highly pipelined and parallel frame processing circuit

- Protocol Control-Path Unit

Data path control, Register and control protocol FIFO circuit

- Embedded Microcontroller Unit Responsible for Control and management protocol processing and Data-Path configuration.

# PPP SoPC System Architecture

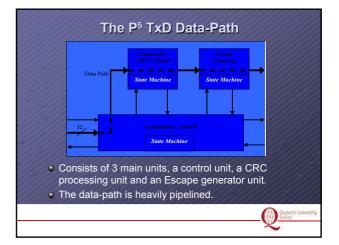

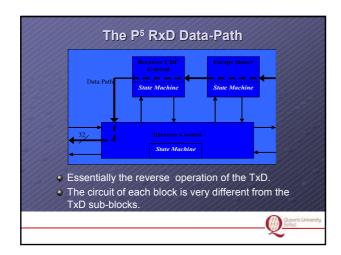

#### P<sup>5</sup> Protocol Data-Path Units

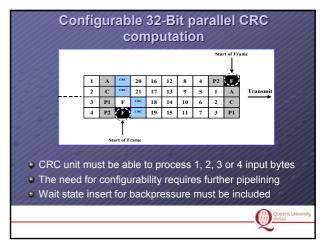

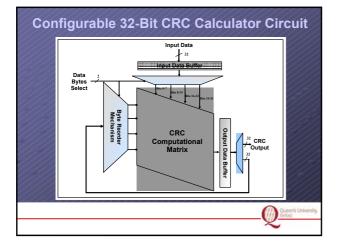

- 32-bit wide circuit. Complete implementation in hardware

- operating at 78.125 Mhz offering a data transfer rate of 2.5 Gbps

- TxD and RxD units are independent, parallel and pipelined

- Focus of presentation is on this unit. 8-bit version has also been implemented

| Data Path | Transmitter<br>CRC Control<br>State Machine                                   | Escape<br>Generate           |

|-----------|-------------------------------------------------------------------------------|------------------------------|

| 32        | Transmitter Contro<br>State Machine                                           |                              |

| Data Path | Receiver CRC<br>Control<br>State Machine<br>Receiver Control<br>State Machine | Escape Detect                |

| /////     |                                                                               | Queen's Universit<br>Boliast |

#### **Embedded Microprocessor Unit** Based on a soft IP core processor (e.g. Nios Microblaze or Leon). Processes the majority of the control and management protocols and control lLeon μP housekeeping functions. AMB BUS Interfaced to a local bus via a standard MEM embedded bus architecture e.g. AMBA All implemented functions are software Peripherals based and can be reprogrammed without interrupting the data transmission path.

#### **Protocol Control-Path Unit**

- Handles the interaction between the embedded processor and the Layer 2 protocol data path

- Composed of an Operation Administration and Maintenance (OAM) unit,

- Accommodates a transmitter and a receiver FIFO for temporary storage of control protocols.

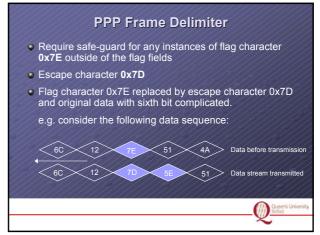

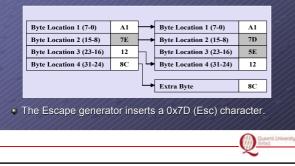

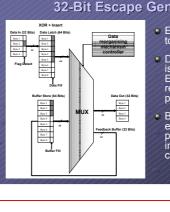

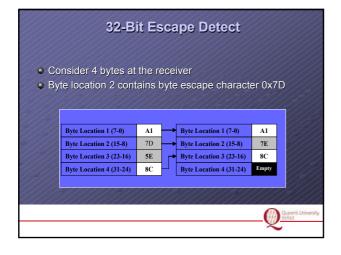

## 32-Bit Escape Generate

- Consider 4 bytes of data to be processed

- Byte location 2 contains a flag character 0x7E

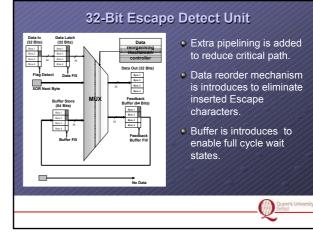

## 32-Bit Escape Generate Circuit

- Extra pipelining is added to reduce critical path.

- Data reorder mechanism is introduces to insert Escape characters and to rearrange the 4 byte data-path frame data.

- Buffer is introduces to enable full cycle back-pressure mechanism after inserting 4 Escape characters.

|         |               | 8 -         | Bit Syste      | m             |               |           |

|---------|---------------|-------------|----------------|---------------|---------------|-----------|

|         | P re -la      | iyout Sy    | nthesis        | Pos           | t-layout      | Synthesis |

| CV50-4  | 95.3<br>M H z | 184<br>LUTs | 84<br>Register | 79.5<br>M H z | 130<br>Slices | 191 LUTs  |

| C2V40-6 | 128.4<br>MHz  | 179<br>LUTs | 84<br>Register | 91.5<br>MHz   | 124<br>Slices | 185 LUTs  |

- 8-bit PPP meets required speed of 78.125 Mhz with Virtex and Virtex II technology

- Virtex II enables considerable speed-up over Virtex.

- Critical paths analysis revealed the same number of LUTs for both technologies. Thus speed-up is achieved because of the technological advantage of Virtex II

|   | Outer's University |

|---|--------------------|

|   | Bellast            |

| X |                    |

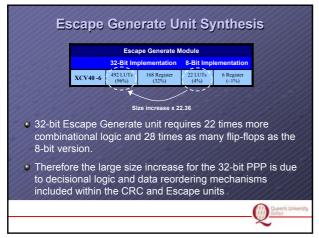

#### 32-Bit System Synthesis Results

|          |                 |                      | 32-Bit System |                       |                |           |

|----------|-----------------|----------------------|---------------|-----------------------|----------------|-----------|

|          | Pre             | Pre-layout Synthesis |               | Post-layout Synthesis |                |           |

| XCV600   | 4 73<br>MHz     | 2641<br>LUTs         | 841 Register  | 65<br>MHz             | 1208<br>Slices | 2563 LUTs |

| XC2V1000 | -6 125.9<br>MHz | 2230<br>LUTs         | 689 Register  | 78.66<br>MHz          | 1144<br>Slices | 2157 LUTs |

- The 32-bit PPP implementation meets the required speed of 78.125 Mhz with Virtex II technology only.

- Again, critical paths analysis revealed the same number of LUTs for both technologies.

- The 32-bit implementation is ×11 times larger than the 8-bit implementation.

### Conclusions

- We have shown that a programmable Layer 2 network processing for 2.5 Gbps throughput rate, including control protocol processing is feasible using the latest SoPC technology.

- The circuit study has revealed that the 32-bit PPP implementation is 11 times larger than 8-bit version.

- Further analysis has shown that this increase is mainly due to the byte sorter and buffering mechanisms included in the 32-bit design which are heavy in combinational logic.

- Programmability of PPP processing is achieved by reconfiguring the programmable logic blocks and by reprogramming the firmware of the embedded processor.

#### **Future Work**

- ASIC Implementation of the current PPP SoPC architecture as a complete SoC (System on a Chip) solution.

- Investigating new technologies and systems architectures for programmable / configurable network processing.

- Investigating trade-offs using off-the-shelf embedded processor and FPGA technology for network processing.

- Development of a new generation of programmable packet processing elements by combining configurable logic with custom processing technology.