This document contains assignments given in LSU EE 4755 over many semesters. It was automatically generated and so some solutions (and possibly some assignments) are likely missing. At the top of each page of each assignment is a link to the original assignment. Those who want to print an assignment might follow that link. All assignments and public solutions are available at https://www.ece.lsu.edu/ee4755/prev.html.

### Contents

| 1 | <b>Fall</b><br>1.1        | <b>2024</b><br>mt.pdf           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | $\frac{4}{5}$ |

|---|---------------------------|---------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---------------|

| 2 | <b>Fall</b><br>2.1<br>2.2 | <b>2023</b><br>mt.pdf<br>fe.pdf |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |               |

| 3 | Fall<br>3.1<br>3.2        | <b>2022</b><br>mt.pdf<br>fe.pdf |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |               |

| 4 | <b>Fall</b><br>4.1<br>4.2 | <b>2021</b><br>mt.pdf<br>fe.pdf |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |               |

| 5 | <b>Fall</b><br>5.1<br>5.2 | <b>2020</b><br>mt.pdf<br>fe.pdf |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |               |

| 6 | <b>Fall</b><br>6.1<br>6.2 | <b>2019</b><br>mt.pdf<br>fe.pdf |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |               |

| 7 | <b>Fall</b><br>7.1<br>7.2 | <b>2018</b><br>mt.pdf<br>fe.pdf |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |               |

| 8 | Fall<br>8.1<br>8.2        | <b>2017</b><br>mt.pdf<br>fe.pdf |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |               |

| 9 | <b>Fall</b><br>9.1<br>9.2 | <b>2016</b><br>mt.pdf<br>fe.pdf |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |               |

| 10 Fall 2015 175                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| 10.1 mt.pdf                                                                                                                                 |

| 10.2 fe.pdf                                                                                                                                 |

|                                                                                                                                             |

| 11 Fall 2014 195                                                                                                                            |

| 11.1 mt.pdf                                                                                                                                 |

| 11.2 fe.pdf $\ldots \ldots 206$                  |

| 12 Spring 2001 216                                                                                                                          |

| 12.1 mt.pdf                                                                                                                                 |

| 12.2 fe.pdf                                                                                                                                 |

|                                                                                                                                             |

| 13 Spring 2000 234                                                                                                                          |

| 13.1 mt.pdf                                                                                                                                 |

| 13.2 fe.pdf                                                                                                                                 |

| 14 Fall 2024 Solutions 252                                                                                                                  |

| 14.1 mt sol.pdf                                                                                                                             |

| 1                                                                                                                                           |

| 15 Fall 2023 Solutions 264                                                                                                                  |

| 15.1 mt sol.pdf $\ldots \ldots 265$       |

| 15.2 fe sol.pdf $\ldots \ldots 274$                                                                                                         |

| 16 Fall 2022 Solutions 283                                                                                                                  |

| 16 Fail 2022 Solutions         283           16.1 mt sol.pdf         284                                                                    |

| 16.2 fe sol.pdf                                                                                                                             |

| 10.2 10 bon.par                                                                                                                             |

| 17 Fall 2021 Solutions 305                                                                                                                  |

| 17.1 mt sol.pdf $\ldots \ldots 306$                            |

| 17.2 fe sol.pdf $\ldots \ldots 322$                                                                                                         |

| 18 Fall 2020 Solutions 339                                                                                                                  |

| 18 Fail 2020 Solutions     339       18.1 mt sol.pdf     340                                                                                |

| 18.2 fe sol.pdf                                                                                                                             |

| 10.2 le soi.pui                                                                                                                             |

| 19 Fall 2019 Solutions 363                                                                                                                  |

| 19.1 mt sol.pdf $\ldots \ldots 364$                                                                                                         |

| 19.2 fe sol.pdf $\ldots \ldots 372$                                                                                                         |

|                                                                                                                                             |

| 20 Fall 2018 Solutions         382           20.1 mt col pdf         282                                                                    |

| $20.1 \text{ mt sol.pdf} \dots \dots$ |

| $20.2 \text{ fe sol.pdf} \dots \dots$ |

| 21 Fall 2017 Solutions 404                                                                                                                  |

| $21.1 \text{ mt sol.pdf} \dots \dots$ |

| 21.2 fe sol.pdf                                                                                                                             |

|                                                                                                                                             |

| <b>22</b> | Fall 2016 Solutions4    | 125 |

|-----------|-------------------------|-----|

|           | 22.1 mt sol.pdf         | 426 |

|           | 22.2 fe sol.pdf         |     |

| 23        |                         | 451 |

|           | 23.1 mt sol.pdf         | 452 |

|           | 23.2 fe sol.pdf         |     |

| <b>24</b> | Fall 2014 Solutions   4 | 473 |

|           | 24.1 mt sol.pdf         | 474 |

|           | 24.2 fe sol.pdf         | 486 |

| <b>25</b> |                         | 198 |

|           | 25.1 mt sol.pdf         | 499 |

|           | 25.2 fe sol.pdf         |     |

| 26        | Spring 2000 Solutions   | 520 |

|           | 26.1 mt sol.pdf         | 521 |

|           | 26.2 fe sol.pdf         |     |

|           | 26.3 fe sol.html        |     |

1 Fall 2024

Name

Formatted For 2-Sided Printing

# Digital Design Using HDLs LSU EE 4755 Midterm Examination

Wednesday, 23 October 2024, 11:30-12:20  $\operatorname{CDT}$

- Problem 1 \_\_\_\_\_ (22 pts)

- Problem 2 \_\_\_\_\_ (18 pts)

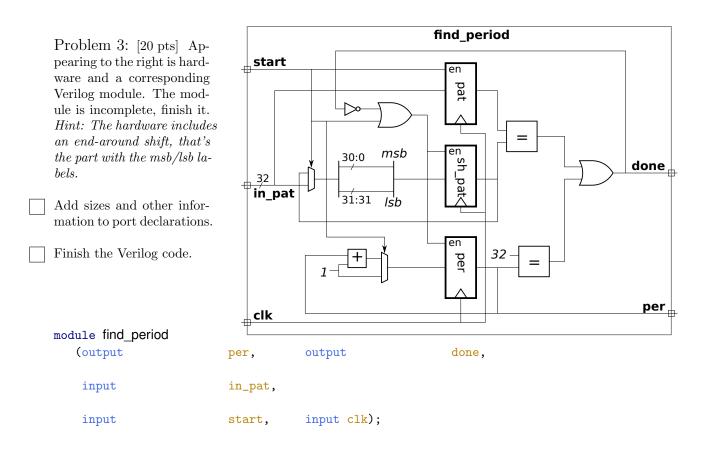

- Problem 3 \_\_\_\_\_ (20 pts)

- Problem 4 \_\_\_\_\_ (10 pts)

- Problem 5 \_\_\_\_\_ (30 pts)

- Exam Total \_\_\_\_\_ (100 pts)

Alias

Good Luck!

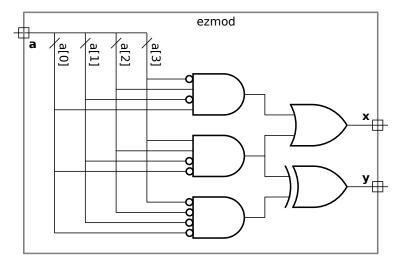

Problem 1: [22 pts] Below is the Homework 3 Problem 1 solution with some object names shortened.

```

typedef enum logic [3:0] {Char_Blank=0, Char_Dot=1, Char_Open=2, Char_Close=3} Char;

module pmatch a #( int n = 5, wn = clog2(n+1) )

( output logic [wn-1:0] lt_un_close, rt_un_open, input uwire [3:0] str[0:n-1] );

if (n == 1) begin

assign lt_un_close = str[0] == Char_Close ? 1 : 0;

assign rt_un_open = str[0] == Char_Open ? 1 : 0;

end else begin

localparam int n_left = n/2;

localparam int n_right = n - n_left;

localparam int wl = $clog2(n_left+1), wr = $clog2(n_right+1);

uwire [wl-1:0] lt_close, lt_open;

uwire [wr-1:0] rt_close, rt_open;

pmatch_base #(n_left, wl) plt( lt_close, lt_open, str[0:n_left-1] );

pmatch_base #(n_right, wr) prt( rt_close, rt_open, str[n_left:n-1] );

uwire logic signed [wn-1:0] delta = lt_open - rt_close;

assign rt_un_open = delta >= 0 ? rt_open + delta : rt_open;

assign lt_un_close = delta < 0 ? lt_close - delta : lt_close;</pre>

end

endmodule

```

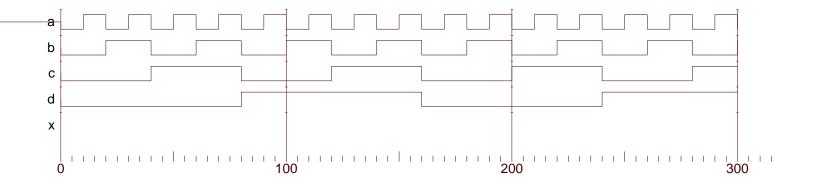

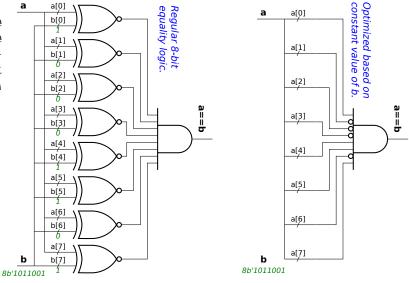

$\left(a\right)$  Show the hardware that will be inferred for the base case. Show hardware after optimization taking into account constants.

Show inferred hardware for base (n==1) case of the module above. Show input and output ports.

Optimize taking into account  $\Box$  constant values of all kinds.  $\Box$  Don't miss the Char definition above the module.  $\Box$  Don't show a comparison unit such as  $\equiv$ , instead show the gates from which it was made and  $\Box$  optimize them,  $\Box$  taking into account the number of bits on each output port.

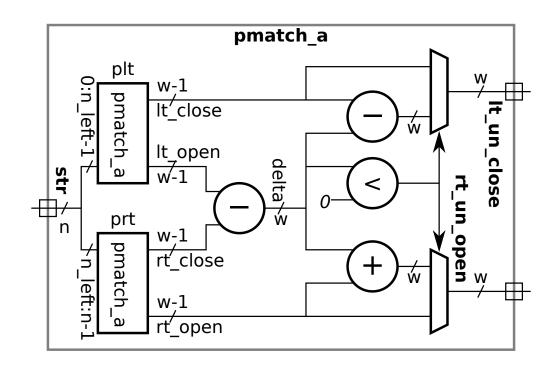

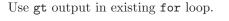

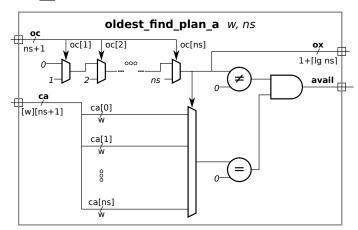

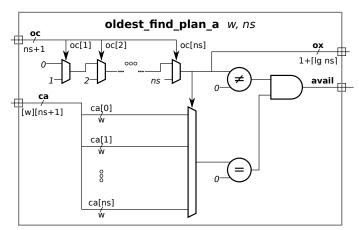

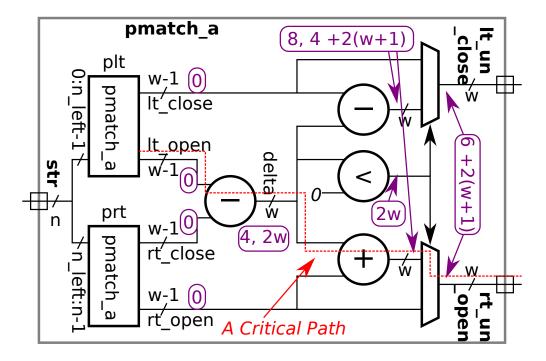

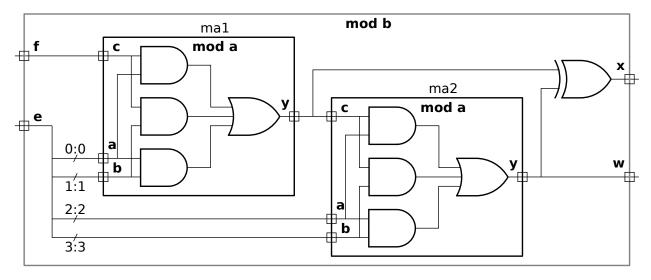

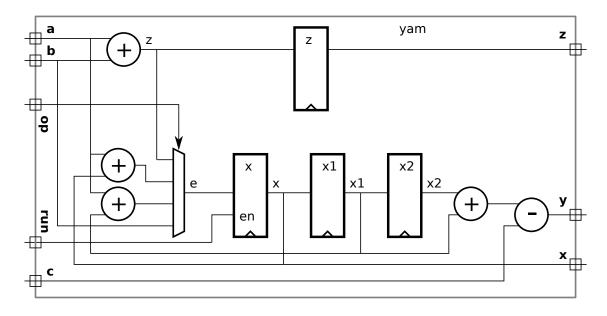

Appearing above is hardware that will be inferred for the non-base case.

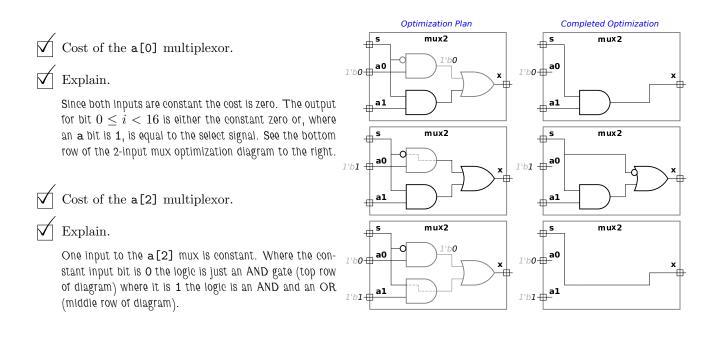

(b) Compute the cost of the hardware at this level (ignore what's inside plt and prt) based on the simple model using the bit widths from the diagram, such as w-1.

Show the cost of each component except for hardware inside of plt and prt.

Be sure to show the cost of the optimized comparison unit!

(c) Compute the delay through the module starting from launch points lt\_close, lt\_open, rt\_close, and rt\_open. The capture points are lt\_un\_close and rt\_un\_open. Use the bit widths from the diagram, such as w-1.

Show the arrival time at each wire from launch to capture.

Take into account cascaded ripple units and  $\Box$  and the optimized comparison unit.

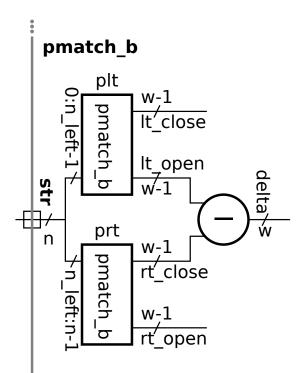

Problem 2: [18 pts] Appearing below is an alternative solution to Homework 3 Problem 1. The only difference is the last few lines.

```

module pmatch_b #( int n = 5, wn = clog2(n+1) )

( output logic [wn-1:0] lt_un_close, rt_un_open,

input uwire [3:0] str[0:n-1] );

if (n == 1) begin

assign lt_un_close = str[0] == Char_Close ? 1 : 0;

assign rt_un_open = str[0] == Char_Open ? 1 : 0;

end else begin

localparam int n_left = n/2;

localparam int n_right = n - n_left;

localparam int wl = $clog2(n_left+1), wr = $clog2(n_right+1);

uwire [wl-1:0] lt_close, lt_open;

uwire [wr-1:0] rt_close, rt_open;

pmatch_base #(n_left, wl) plt( lt_close, lt_open, str[0:n_left-1] );

pmatch_base #(n_right, wr) prt( rt_close, rt_open, str[n_left:n-1] );

uwire logic signed [wn-1:0] delta = lt_open - rt_close;

// Lines above are identical to pmatch_a.

uwire [wn-1:0] delta_p = delta > 0 ? delta : 0;

uwire [wn-1:0] delta_n = delta <= 0 ? delta : 0;</pre>

assign rt_un_open = rt_open + delta_p;

assign lt_un_close = lt_close - delta_n;

end

endmodule

```

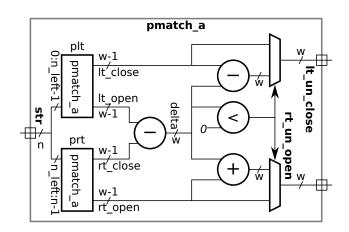

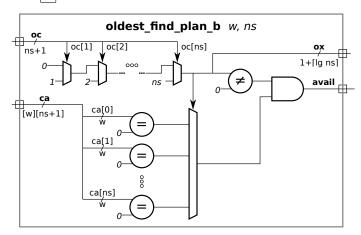

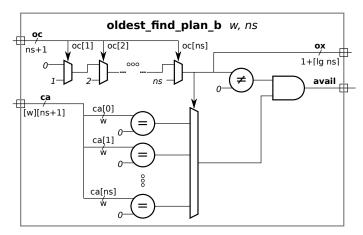

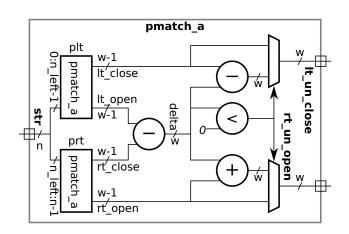

(a) Show the hardware that will be inferred for pmatch\_b. For your convenience the hardware for pmatch\_a is shown in the upper right.

Show inferred hardware on the facing page.

(b) Compute the simple-model cost of the hardware.

Write <u>same</u> next to components that cost the same as corresponding components in pmatch\_a and \_\_\_\_\_ compute the cost of other components \_\_\_\_\_\_ after optimization.

$\left( c\right)$  Compare the critical path lengths.

Will the critical path in pmatch\_a be much different than the one in pmatch\_b?

Explain.

$\leftarrow \ \rightarrow \ {\rm Midterm} \ {\rm Exam}$

Staple This Side

Problem 3: [20 pts] Appearing below are some of the dot modules from the solution to Homework 1. On the facing page is incomplete module dotn. Complete dotn so that it describes hardware that computes the dot product of n-element vectors recursively, where n is the parameter. That is, dotn must instantiate dotn and should instantiate mult and add where needed.

```

module mult #( int w = 5 ) ( output uwire [w-1:0] p, input uwire [w-1:0] a, b );

assign p = a * b;

endmodule

module add #( int w = 5 ) ( output uwire [w-1:0] s, input uwire [w-1:0] a, b );

assign s = a + b;

endmodule

module dot2 #( int w = 5 )

( output uwire [w-1:0] dp,

input uwire [w-1:0] a[1:0], b[1:0] );

// Computes dp = a[0] * b[0] + a[1] * b[1];

uwire [w-1:0] p0, p1;

mult #(w) m0(p0, a[0], b[0] );

mult #(w) m1(p1, a[1], b[1] );

add #(w) ad(dp, p0, p1 );

endmodule

module dot3 #( int w = 5 )

( output uwire [w-1:0] dp, input uwire [w-1:0] a[2:0], b[2:0] );

// Computes dp = a[0] * b[0] + a[1] * b[1] + a[2] * b[2];

uwire [w-1:0] p0, p2;

dot2 #(w) d0( p0, a[1:0], b[1:0] );

mult #(w) m2( p2, a[2], b[2] );

add #(w) a2(dp, p0, p2);

endmodule

```

Complete dotn so that it describes tree-structured hardware computing an n-element dot product. The tree depth should be  $\lceil \lg n \rceil$ .

Instantiate mult for multiplication and add for addition, and of course dotn for a dot product of a smaller vector.

] To keep things easy all wires are w bits.

#### module dotn

```

#( int w = 5, n = 4 )

( output uwire [w-1:0] dp,

input uwire [w-1:0] a[n-1:0], b[n-1:0] );

```

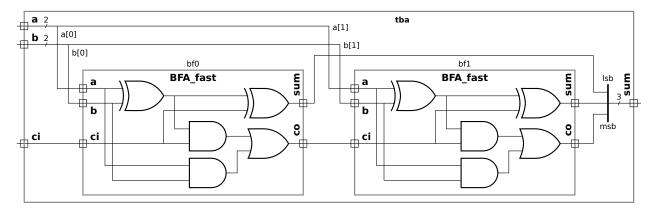

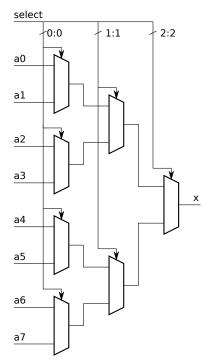

Problem 4: [10 pts] Appearing below is the logarithmic shifter presented in class, followed by a version that's supposed to be better (but isn't). The hoped-for improvement is due to instantiating the exact number of multiplexors (muxw2) needed, rather than enough for the maximum shift amount.

```

module shift right logarithmic #( int w = 16, lgw = clog2(w) )

( output uwire [w-1:0] shifted,

input uwire [w-1:0] un,

input uwire [lgw-1:0] amt );

// This module is correct.

uwire [w-1:0] s[lgw:-1];

assign s[-1] = un;

for ( genvar i=0; i<lgw; i++ )</pre>

muxw2 #(w) st(s[i], amt[i], s[i-1], s[i-1] >> (1 << i) );</pre>

assign shifted = s[lgw-1];

endmodule

module shift_right_logarithmic_better_maybe #( int w = 16, lgw = $clog2(w) )

( output uwire [w-1:0] shifted,

input uwire [w-1:0] un, input uwire [lgw-1:0] amt );

uwire [w-1:0] s[lgw:-1];

assign s[-1] = un;

// Use exactly the number of stages needed!!!

uwire [lgw-1:0] lg_amt;

// LINE ADDED

my_clog2 #(lgw) mc( lg_amt, amt ); // LINE ADDED. Set lg_amt = $clog2(amt) = [lgamt];

for ( genvar i=0; i<lg_amt; i++ )</pre>

// LINE DIFFERS

muxw2 #(w) st( s[i], amt[i], s[i-1], s[i-1] >> ( 1 << i ) );</pre>

assign shifted = s[lg_amt-1];

// LINE DIFFERS

endmodule

```

Why won't the Verilog above compile?

Is it possible to fix the Verilog error in such a way that cost is lower with smaller shift amounts?

Is it possible to fix the Verilog error in such a way that the delay reported by a synthesis program is lower? Explain.

Is it possible to fix the Verilog error in such a way that the delay actually is lower?  $\Box$  Explain.

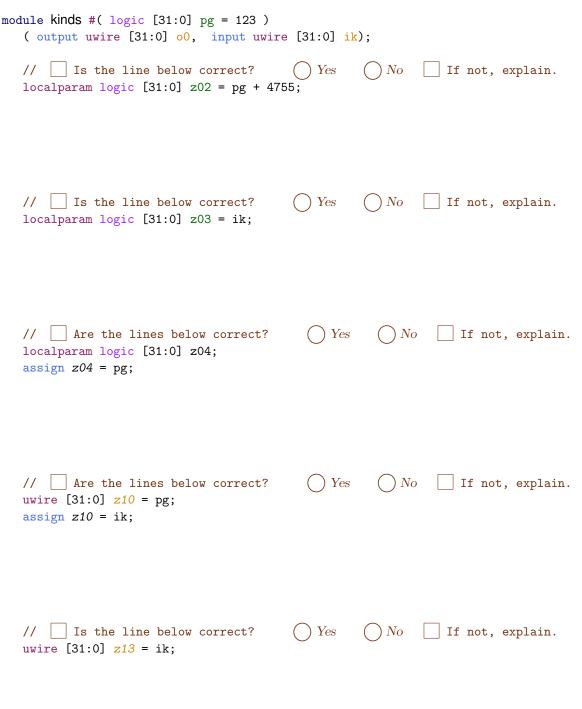

Problem 5: [30 pts] Answer the following Verilog questions.

(a) The module below uses multidimensional arrays. module mda( input uwire [2:1] c [5:1], input uwire [7:1][2:1] a [5:1][3:1] ); // Add dimension(s) to the declaration of e so that the assignment is correct. 11 = c; uwire е 11 Add dimension(s) to the declaration of b so that the assignment is correct. 11 = a[1][1][1]; uwire b logic g [7:0]; logic [7:0] h; initial begin () both () only the assignment to g, () only the assignment to h, or // Which is correct, are correct. Explain. g[1] = h[1];h[1] = g[1];end endmodule

What is the size of c, in bits? What is the size of a, in bits?

$\left(b\right)$  In the module below indicate whether each code fragment is correct.

endmodule

(c) When we run a synthesis program we specify a delay target. In class we often synthesize twice, once with a delay target of 100 ns and a second time with a target of 0.1 ns. What is the harm in specifying a delay target lower (faster) than one needs? Isn't faster better?

Harm in setting delay target too low is:

(d) A 32-bit signed integer, say i, is converted into a 32-bit IEEE 754 floating-point format (8-bit exponent, 23-bit significand) and then back into a 32-bit integer, j.

Is it guaranteed that i = j for all  $-2^{31} \le i < 2^{31}$ ? Explain based on the FP representation.

2 Fall 2023

Name

Digital Design Using HDLs LSU EE 4755 Midterm Examination Friday, 27 October 2023, 11:30-12:20 CDT

- Problem 1 \_\_\_\_\_ (30 pts)

- Problem 2 \_\_\_\_\_ (25 pts)

- Problem 3 \_\_\_\_\_ (30 pts)

- Problem 4 \_\_\_\_\_ (15 pts)

- Exam Total \_\_\_\_\_ (100 pts)

Alias

Good Luck!

Staple This Side

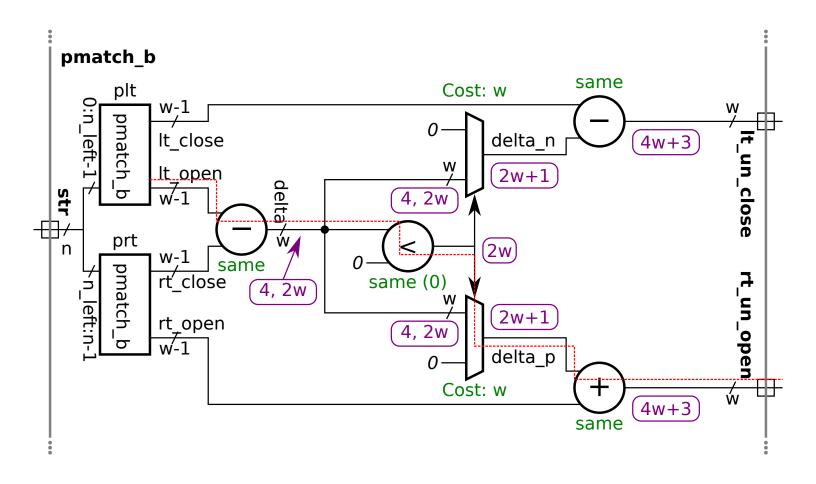

Problem 1: [30 pts] Appearing below is the permutation module from the solution to Homework 3. Using the illustration of the ports show the inferred hardware for an instantiation with n=4. Show the n=3 recursive instantiation.

```

module perm

#( int w = 8, n = 20, wd = (100) = (100)

( output uwire [w-1:0] pdata_out[n],

output uwire [wd-1:0] pnum_out[n],

output uwire carry_out,

input uwire [w-1:0] pdata_in[n],

input uwire [wd-1:0] pnum_in[n] );

if (n == 1) begin

assign pdata_out[0] = pdata_in[0];

assign carry_out = 1;

assign pnum_out[0] = 0;

end else begin

uwire [wd-1:0] pos = n - 1 - pnum_in[n-1];

assign pdata_out[n-1] = pdata_in[pos];

uwire [w-1:0] prdata_in[n-1];

for ( genvar i=0; i<n-1; i++ )</pre>

assign prdata_in[i] = i < pos ? pdata_in[i] : pdata_in[i+1];</pre>

uwire co;

perm #(w,n-1,wd) rp( pdata_out[0:n-2], pnum_out[0:n-2], co,

pdata_in[0]

prdata_in, pnum_in[0:n-2] );

[1]

uwire [wd-1:0] dnext = pnum_in[n-1] + co;

[2]

assign carry_out = dnext >= n;

pdata_

assign pnum_out[n-1] = carry_out ? 0 : dnext;

[3]

end

endmodule

```

Show inferred hardware for n=4. Be sure to use the illustrated module ports and to show the recursively instantiated module (but not its contents).

Show hardware, 🔲 do not confuse elaboration-time computation with computation hardware.

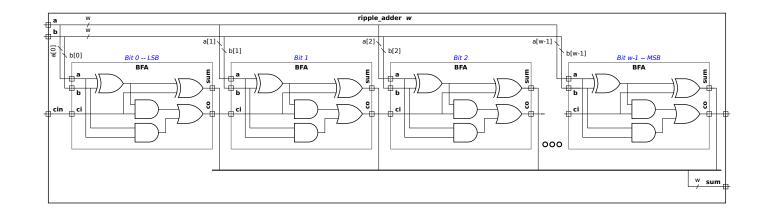

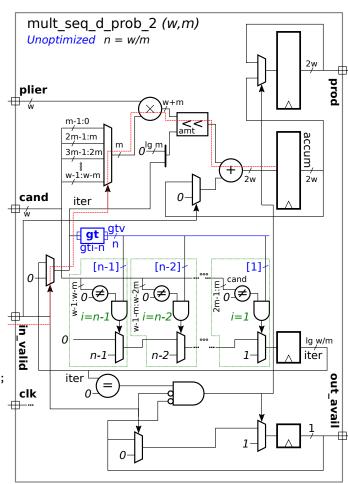

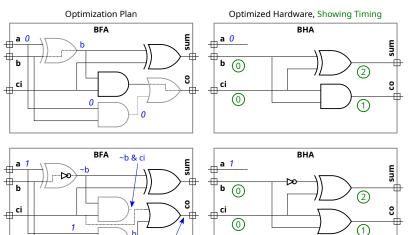

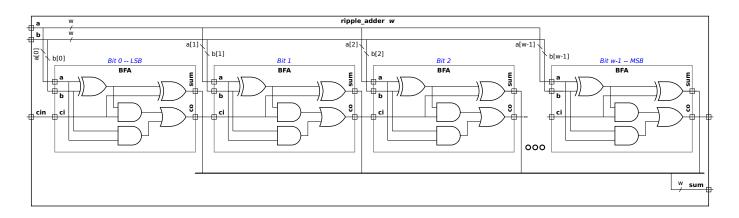

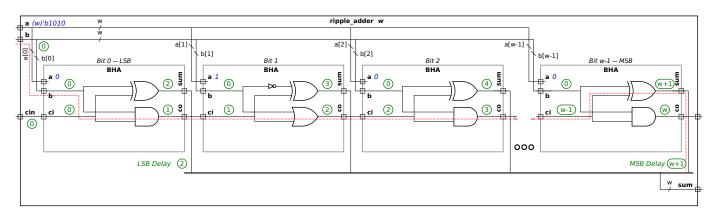

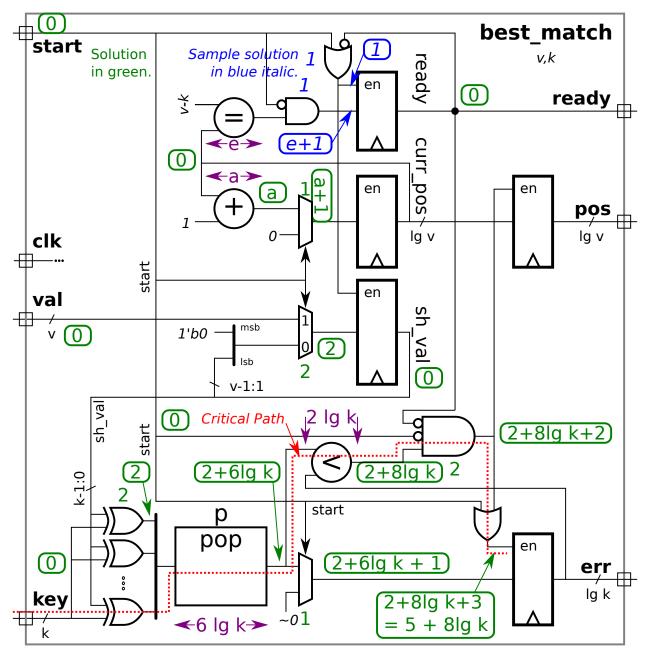

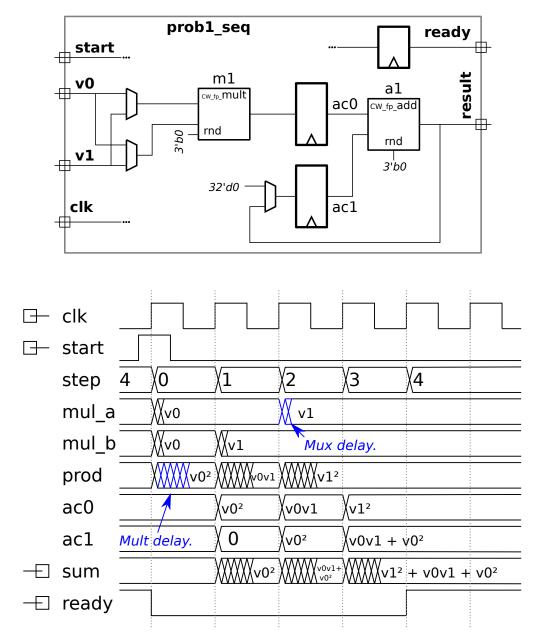

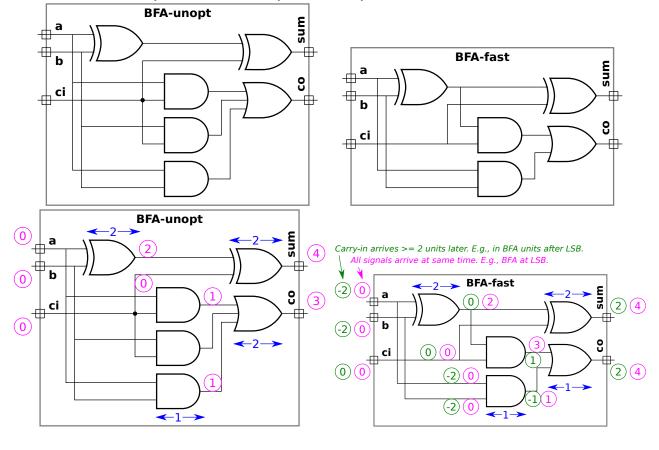

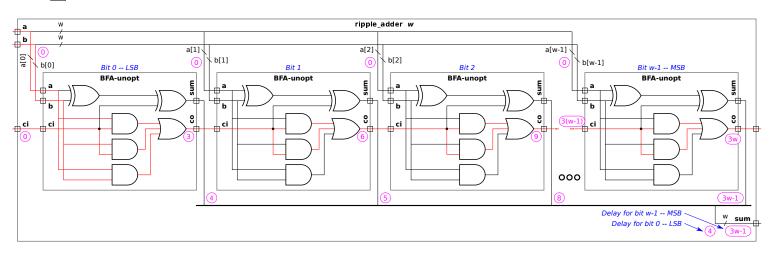

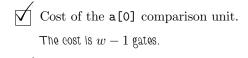

Problem 2: [25 pts] A ripple adder to compute a + b is to be used in situations where a is a constant.

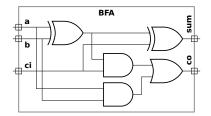

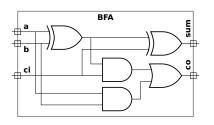

(a) Find the cost and delay of a BFA with input a constant (for use in the ripple adder). A BFA is shown for your convenience.

Show the BFA(s) optimized for input *a* constant.

Use a truth table to find optimizations not revealed by constant pushing: in a correct solution the delay does not depend upon **a**.

Show simple-model cost of this (these) module (s) and [ ] show simple-model delay (s) of this (these) module (s).

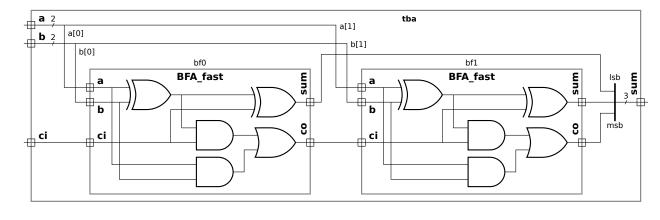

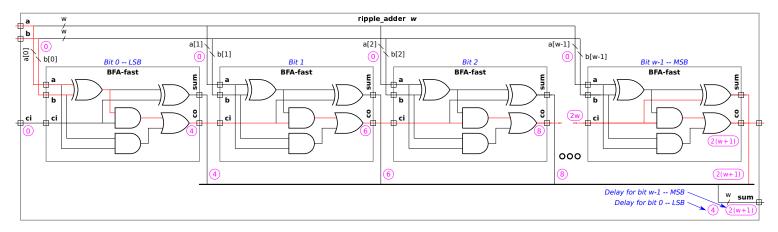

(b) On the facing page show the optimized hardware, cost, LSB delay, and MSB delay of a *w*-bit ripple adder for computing  $a + b + c_{in}$ , where  $c_{in}$  is a carry-in bit (cin in the diagram) and *a* is a constant. ( See the check box items for details.) Use the illustration on the facing page as a starting point.

Compute the simple-model cost of this hardware in terms of w.

Compute the simple-model delay of the LSB of the sum.

Compute the simple-model delay of the MSB of the sum in terms of w and  $\square$  show the critical path.

Don't forget that **a** is a constant.

Staple This Side

(c) If cin were removed (or set to zero) the cost and delay of the optimized adder would depend on a. Explain why, and illustrate with the example of a=2.

How are cost and delay dependent on a when cin removed? Explain using the example a=2.

Problem 3: [30 pts] Answer the following Verilog questions.

(a) The module below makes extensive use of multidimensional arrays.

```

input uwire [7:1][2:1] a [5:1][3:1] );

module mda( input uwire [2:1] c [5:1],

11

Add dimension(s) to the declaration of e so that the assignment is correct.

11

= c[1];

uwire

е

Add dimension(s) to the declaration of b so that the assignment is correct.

11

11

= a[1];

uwire

b

logic g [7:0];

logic [7:0] h;

initial begin

\bigcirc the assignment to g or

() the assignment to h.

// Which is correct,

Explain.

g = 1;

h = 1;

end

endmodule

```

What is the size of c, in bits? What is the size of a, in bits?

(b) The module below does not compile.

```

module more_stuff #( int n = 20 ) ( output uwire [31:0] sum, input uwire [31:0] a [ n ] );

logic [31:0] acc;

always_comb begin

acc = a[0];

for ( int i=1; i<n; i++ )

my_fixed_adder al(acc, acc, a[i] );

end

assign sum = acc;

endmodule

```

Describe the major problem.  $\square$  **DO NOT** try to fix the problem.

```

(c) The module below is supposed to set x = a<sup>2</sup> + b<sup>2</sup>.

module wrong_way( output logic [31:0] x, input uwire [15:0] a, b );

logic [31:0] asq;

uwire [31:0] bsq = b * b;

initial asq = a * a;

always_comb x = asq + bsq;

endmodule

```

Explain the problem. Using sample inputs show the expected output and the actual output.

Fix the problem.

(d) The module below does not compile.

```

module my_adder( output uwire [31:0] s, input uwire [31:0] a, b );

always_comb s = a + b;

endmodule

```

Why won't module above compile? \_\_\_\_ Fix problem by changing declarations.

(e) The module below compiles but does not provide the expected outputs,  $p_a = a^2$ ,  $p_b = b^2$ , and  $p = a^2 + b^2$ .

```

module incorrect_way( output logic [31:0] pa,pb,p, input uwire [15:0] a, b );

wire [31:0] sq;

assign sq = a * a;

always_comb pa = sq;

assign sq = b * b;

always_comb pb = sq;

always_comb p = pa + pb;

endmodule

```

What will be the values of outputs **pa**, **pb**, and **p**?

Describe the problem. Fix it.

Problem 4: [15 pts] Answer each question below.

(a) A company has two teams, A (very good) and C (slackers) working on modules and a testbench for an important product. Describe the following consequences:

The A team works on the modules and the C team works on the testbench. A possible bad outcome is:

The A team works on the test bench and the C team works on the modules. A possible bad outcome is:

(b) In typical use when running simulation a testbench generates inputs for a module-under-test and the outputs are checked by the testbench to see whether they are correct. After running synthesis we learn how fast the module is. If simulation is computing the module outputs why can't it tell us how fast the module is?

Synthesis can provide timing information and simulation can't because:

$\left(c\right)$  A gadget can be built using an ASIC or an FPGA. Describe which is more appropriate for each situation below.

| The gadget must be working within a month. | $\bigcirc ASIC$ or | $\bigcirc$ FPGA. | Explain. |

|--------------------------------------------|--------------------|------------------|----------|

|--------------------------------------------|--------------------|------------------|----------|

|                                                              | $\sim$     | $\frown$ |         |

|--------------------------------------------------------------|------------|----------|---------|

| Per-gadget cost must be under \$1000. Only ten will be made. | () ASIC or | () FPCA  | Evplain |

| rei-gauget cost must be under \$1000. Only ten win be made.  |            |          |         |

Per-gadget cost must be under \$100. Ten thousand will be made.  $\bigcirc ASIC$  or  $\bigcirc FPGA$ .  $\square$  Explain.

Name \_

### Digital Design using HDLs LSU EE 4755 Final Examination

Thursday, 7 December 2023 15:00-17:00 CST

- Problem 1 \_\_\_\_\_ (28 pts)

- Problem 2 \_\_\_\_\_ (25 pts)

- Problem 3 \_\_\_\_\_ (27 pts)

- Problem 4 \_\_\_\_\_ (20 pts)

- Exam Total \_\_\_\_\_ (100 pts)

Alias

Good Luck!

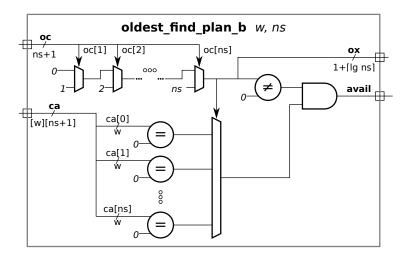

Problem 1: [28 pts] Appearing below is the solution to Homework 5.

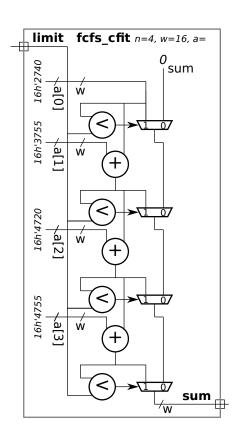

(a) On the facing page show the inferred hardware for an instantiation with n=4.

(b) Explain why the cost of the hardware corresponding to the line  $n_match += match$  is much lower than one would expect for hardware performing wc-bit addition.

The n\_match += match is much less expensive because:

```

module uniq_vector_seq

\#( int we = 10, n = 4, wc = \frac{100}{2}(n+1) )

( output logic [n-1:0] uniq_bvec,

output logic [wc-1:0] n_match,

input uwire [we-1:0] element,

input uwire start, clk );

logic [we-1:0] elements [n-1:0];

logic [n-1:0] occ_bvec;

logic [wc-1:0] uniq_at [n-1:0];

always_ff @( posedge clk ) begin

automatic logic [wc-1:0] match_pos = n;

n_match = 1;

for ( int i=n-1; i>=1; i-- ) begin

automatic logic next_occ_bvec = !start && occ_bvec[i-1];

automatic logic match = next_occ_bvec && element == elements[i-1];

n_match += match;

if ( match ) match_pos = i;

elements[i] <= elements[i-1];</pre>

occ_bvec[i] <= next_occ_bvec;</pre>

uniq_at[i] <= match ? n : uniq_at[i-1];</pre>

uniq_bvec[i] <= !next_occ_bvec || !match && i >= uniq_at[i-1];

end

elements[0] <= element;</pre>

occ_bvec[0] <= 1;

uniq_at[0] <= n - match_pos;</pre>

uniq_bvec[0] <= match_pos == n;</pre>

end

```

```

endmodule

```

Show inferred hardware for n=4.

Do not confuse ports with parameters. Do not confuse elaboration-time computation with computation hardware.

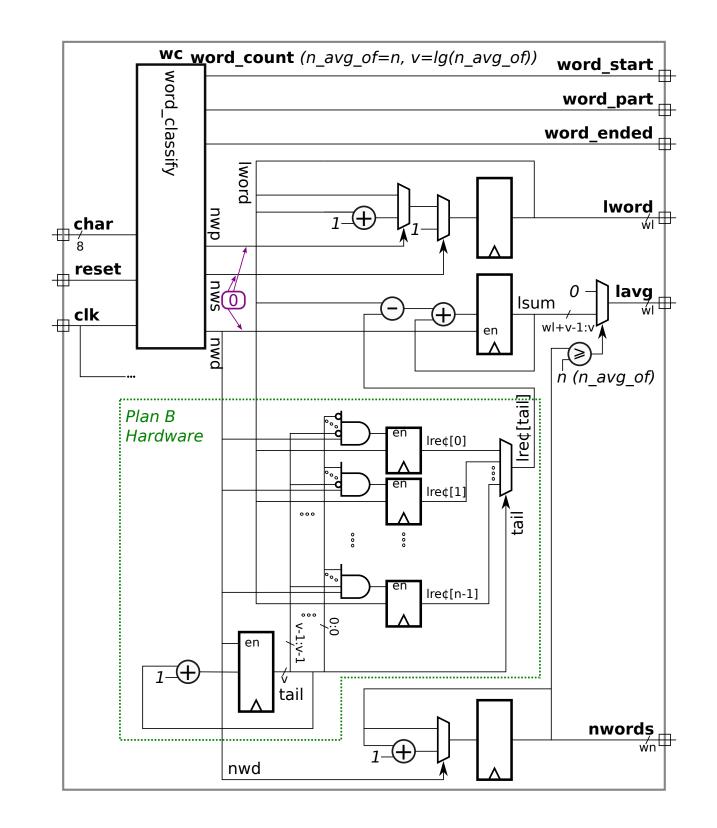

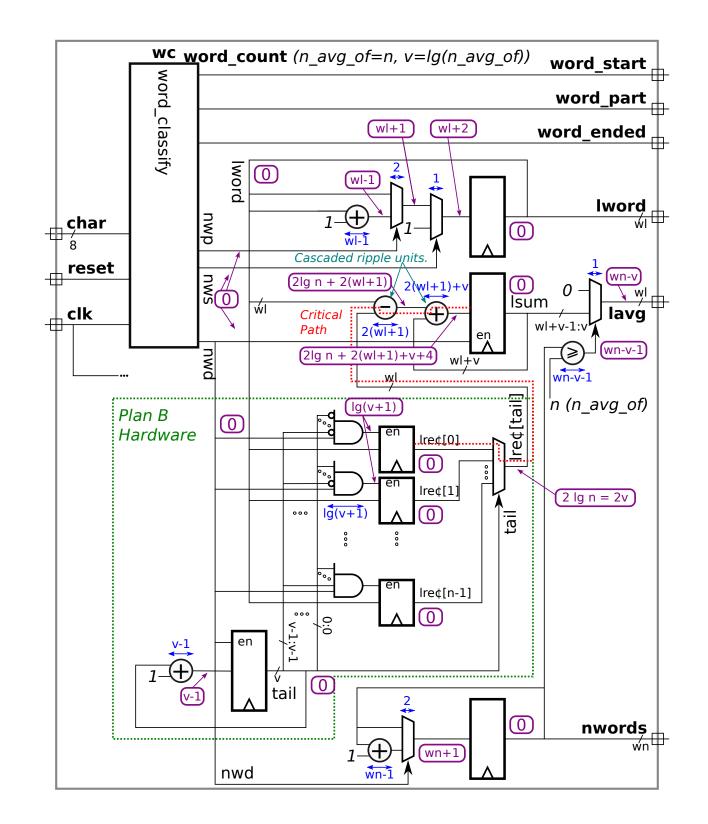

Problem 2: [25 pts] Illustrated on the facing page is a diagram showing inferred hardware similar to the word\_count module from last year's final exam. An important difference is that it is shown for n\_avg\_of=n, not the specific value of 4. Assume that n is a power of 2.

In terms of n, wl, wn, and v show simple-model arrival times at each wire and  $\Box$  show a critical path.

Account for cascaded ripple units constant inputs, and remember that **n** can be any power of 2, not neccessarily 4.

In terms of n, wl, wn, and v compute the simple-model cost of the Plan B hardware, assuming n is a power of 2.  $\Box$  Account for constant inputs.

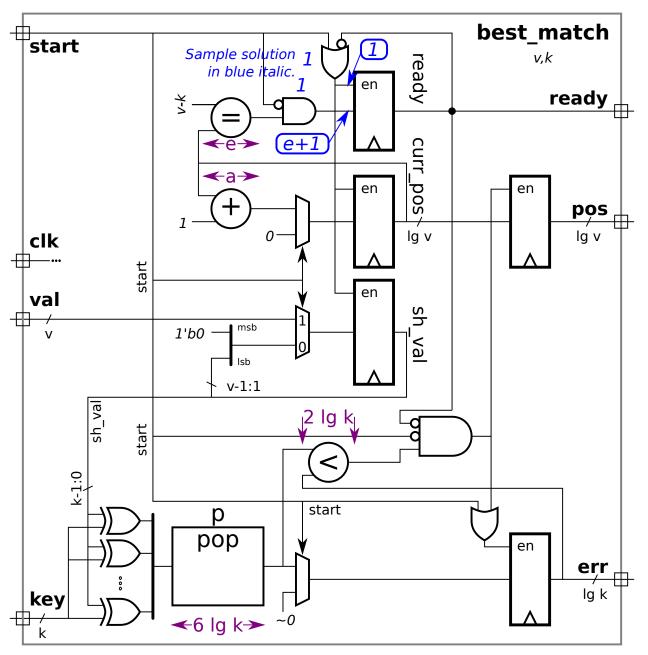

Problem 3: [27 pts] The two modules below look for a match of input target in an n-element array elts but only check elements 0 to i\_limit-1. Output n\_match is the number of matching elements and match\_i is the lowest i for which elts[i]==target and i<i\_limit, or n if there is no match. (These modules could be used in the uniq\_vector module.) Module fmatch\_comb is complete and works correctly.

(a) Module fmatch\_rec has some code for a recursive implementation. Complete it so that it performs the same calculation as fmatch\_comb.

Complete fmatch\_rec so that it computes the same values as fmatch\_comb.

Don't forget to show the bit ranges of **elts** in the connections to the recursive instantiations.

```

module fmatch_comb

#( int n = 22, w = 12, wn = $clog2(n+1) )

( output logic [wn-1:0] n_match, match_i,

input uwire [w-1:0] elts[n-1:0], target, input uwire [wn-1:0] i_limit );

// Do not modify this module. It is correct.

always_comb begin

n_match = 0;

match_i = n;

for ( int i=n-1; i>=0; i-- ) if ( i < i_limit && elts[i] == target ) begin

n_match++;

match_i = i;

end

end</pre>

```

endmodule

```

module fmatch rec

\#( int n = 22, w = 12, wn = \frac{c\log^2(n+1)}{}

( output uwire [wn-1:0] n_match, match_i,

input uwire [w-1:0] elts[n-1:0], target,

input uwire [wn-1:0] i_limit );

if ( n == 1 ) begin

// Do not modify the n==1 code, it works.

uwire match = i_limit != 0 && elts[0] == target;

assign n_match = match;

assign match_i = match ? 0 : 1;

end else begin

localparam int nlo =

localparam int nhi =

localparam int wnr = $clog2(nhi);

uwire [wnr-1:0] nm_lo, nm_hi, mi_lo, mi_hi;

uwire [wnr-1:0] il_lo =

uwire [wnr-1:0] il_hi =

fmatch_rec #(nlo,w,wnr) ilo( nm_lo, mi_lo, elts[

], target, il_lo );

11

Show elts' bit ranges \uparrow\uparrow\downarrow\downarrow\downarrow

fmatch_rec #(nhi,w,wnr) ihi( nm_hi, mi_hi, elts[

], target, il_hi )

assign n_match =

```

assign match\_i =

end

endmodule

Problem 4: [20 pts] Answer each question below.

(a) Consider two technology targets, FabFab A1000, an ASIC, and LÜTeq FXL9000, an FPGA. Floating-point multipliers are available on the A1000 and the FXL9000 targets.

On one of these targets a design can have as many multipliers as will fit on the chip. Which target is it? Explain.

On the other target there is a fixed number of FP multipliers, say 5. Does that mean a design that needs 7 FP multipliers can't use the target?

Explain.

The number of needed multipliers can't be reduced.

(b) The output of the module below will be lt=1 for inputs a=100, b=40, amt=20, indicating that 100+40 < 20, which is wrong of course. It works correctly for a=100, b=40, amt=5, meaning the output is lt=0.

```

module less_than( output uwire lt, input uwire [6:0] a, b, amt );

assign lt = a + b < amt;

endmodule</pre>

```

Why is the output wrong?

What is the largest value of amt for which the module output is correct when the other inputs are a=100, b=40?

(c) The hw output of the module below is supposed to be set to the number of 1s in input vec at the positive edge of the clock. Due to a beginner's Verilog error it does not work.

```

module pop #( int n = 5, wn = $clog2(n+1) )

( output logic [wn-1:0] hw, input uwire [n-1:0] vec, input uwire clk );

always_ff @( posedge clk ) begin

hw <= 0;

for ( int i=0; i<n; i++ ) hw <= hw + vec[i];

end

endmodule</pre>

```

Describe the problem. Describe how it's possible that hw can be greater than n with this error. Fix the problem.

(d) Consider the population module below.

```

module pop_comb #( int n = 5, wn = $clog2(n+1) )

( output logic [wn-1:0] hw, input uwire [n-1:0] vec );

always_comb begin

hw = 0;

for ( int i=0; i<n; i++ ) hw = hw + vec[i];

end

endmodule</pre>

```

The loop above is procedural. Re-write the module below so that it is a generate loop. The array  ${\tt s}$  should come in handy.

```

module pop_comb #( int n = 5, wn = $clog2(n+1) )

( output uwire [wn-1:0] hw, input uwire [n-1:0] vec );

uwire [wn-1:0] s [n-1:0];

```

3 Fall 2022

Name

Formatted For 2-Sided Printing

## Digital Design Using HDLs LSU EE 4755 Midterm Examination

Wednesday, 19 October 2022, 11:30-12:20 CDT

Problem 1 \_\_\_\_\_ (25 pts)

- Problem 2 \_\_\_\_\_ (31 pts)

- Problem 3 \_\_\_\_\_ (20 pts)

- Problem 4 \_\_\_\_\_ (12 pts)

- Problem 5 (12 pts)

Exam Total \_\_\_\_\_ (100 pts)

Alias

Good Luck!

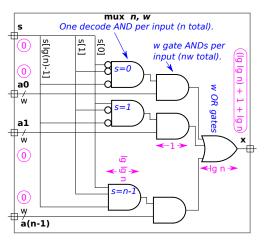

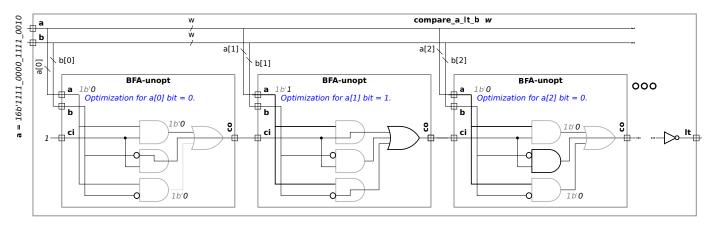

Problem 1: [25 pts] Answer the following multiplexor questions.

(a) Complete module mux4 so that it implements a 4-input multiplexor using instantiations of the 2-input multiplexor shown below. Do not use procedural code.

Complete mux4 so that it implements a 4-input multiplexor 🗌 using mux2 instantiations.

Do not use procedural code. Do not change the ports or default parameters of mux4 or mux2.

Don't forget to declare any objects that are used.

endmodule

```

module mux2

#( int w = 6 )

( output uwire [w-1:0] x,

input uwire s, input uwire [w-1:0] a0, a1 );

assign x = s ? a1 : a0;

endmodule

```

(b) Module mux2\_bad only works for w=1. Describe the problem and show the correct mux output and the output of mux2\_bad for w=4, s=0, a0=2, and a1=4.

```

module mux2_bad

#( int w = 4 )

( output uwire [w-1:0] x,

input uwire s, input uwire [w-1:0] a0, a1 );

assign x = !s && a0 || s && a1;

endmodule

] In mux2 (a correct mux) when w=4, s=0, a0=2, and a1=4, _____ output x=

] In mux2_bad when w=4, s=0, a0=2, and a1=4, _____ output x=

```

Explain the problem when w is not 1.

(c) Complete module  $mux2_1r$  below so that it recursively implements a 2-input w-bit mux. All that remains to be done is completing the connections to the two recursive instances, m1 and mr.

```

module mux2_1r

#( int w = 5 )

( output uwire [w-1:0] x,

input uwire s, input uwire [w-1:0] a0, a1 );

if ( w == 1 ) begin

assign x = !s && a0 || s && a1;

end else begin

mux2_1r #(1) m1(

mux2_1r #(w-1) mr(

end

```

endmodule

Staple This Side

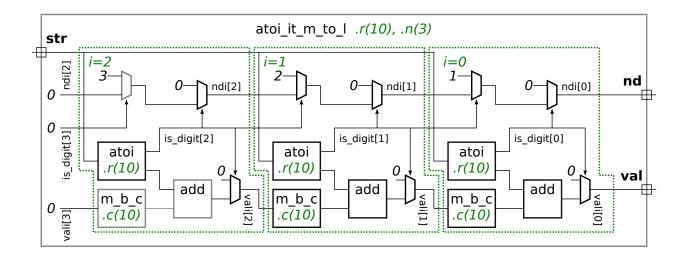

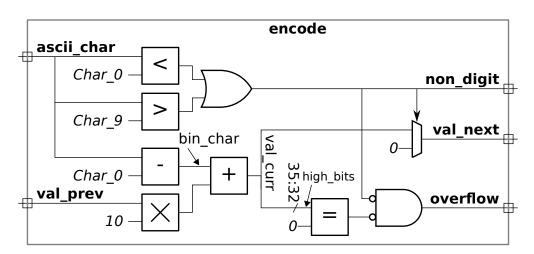

Problem 2: [31 pts] The val output of atoi\_it\_m\_to\_l is the value of the radix-r ASCII-represented number appearing at its input, str, and output nd is the number of digits. Unlike the Homework 2 Problem 2 module, this module starts at the most-significant digit rather than the least-significant digit.

```

module atoi it m to l

#( int r = 11, n = 5, wv = $clog2( r**n ), wd = $clog2(n+1) )

( output logic [wv-1:0] val,

output logic [wd-1:0] nd,

input uwire [7:0] str [n-1:0] );

uwire [wv-1:0] vali[n:0];

uwire is_digit[n:0];

uwire [wd-1:0] ndi[n:0];

assign is_digit[n] = 0;

assign ndi[n] = 0;

assign vali[n] = 0;

assign nd = ndi[0];

assign val = vali[0];

localparam int wcv = $clog2(r);

for ( genvar i=n-1; i>=0; i-- ) begin

// Find Value of Digit i

uwire [wcv-1:0] vald;

atoi1 #(r,wcv) a( vald, is_digit[i], str[i] );

// Multiply (scale) the accumulated sum.

uwire [wv-1:0] valns;

mult_by_c #( .w_in(wv), .c(r), .w_out(wv) ) mc( valns, vali[i+1] );

// Update accumulated value.

assign vali[i] = is_digit[i] ? valns + vald : 0;

// Update number of digits.

assign ndi[i] = !is_digit[i] ? 0 : is_digit[i+1] ? ndi[i+1] : i + 1;

```

end

### endmodule

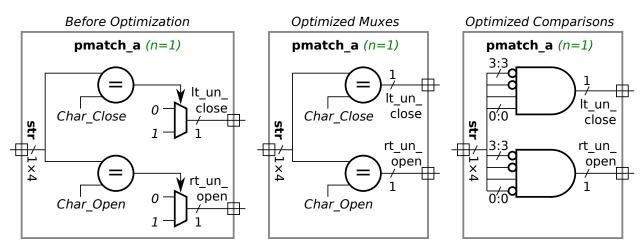

(a) Describe how the behavior of the module would change if the loop direction were changed as shown below, but no other changes were made.

for ( genvar i=0; i<n; i++ ) begin</pre>

Change in behavior with ascending loop:

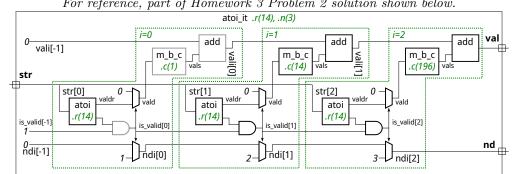

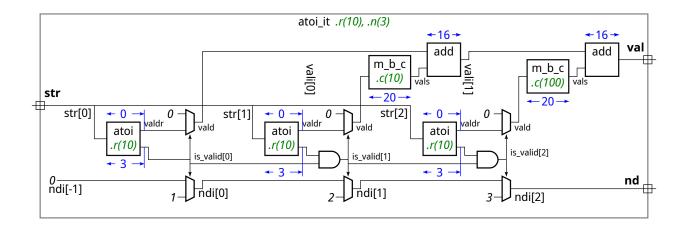

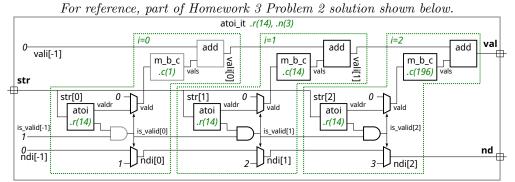

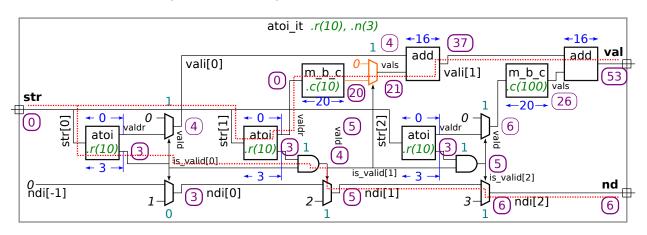

(b) On the next (facing) page show the hardware that will be inferred for an instantiation of atoi\_it\_m\_to\_l (descending loop version) with n=3 and r=10. Show each instantiation of atoi1 and mult\_by\_c as a box, do not show their contents. The inferred hardware for atoi\_it is shown for reference.

For reference, part of Homework 3 Problem 2 solution shown below.

For reference, part of Homework 3 Problem 2 solution shown above.

Show inferred hardware for atoi\_it\_m\_to\_l for n=3 and r=10.

Show the hardware inferred for the operators, such as && and ?:.

Do not confuse parameters and ports and omit hardware that does not belong, such as "hardware" to compute values needed at elaboration time.

(c) Module atoi\_m\_to\_1 will only show the value of numbers that are right-aligned in str, otherwise the value will be shown as zero. For example, for input str="\_\_123" the output would be val=123 and nd=3, but for input str="\_123\_" the output would be val=0 (because the rightmost character is not a digit). Modify the module so the val output is the value of the number regardless of its location. If there is more than one number, say str="\_\_12\_345\_", show the value of the rightmost number, 345 in this case.

Modify so that val and nd are for numbers whether or not they are right-aligned.

Do not use procedural code.

Avoid costly or slow solutions.

A correct solution only requires a few changes.

module atoi\_it\_m\_to\_l

```

#( int r = 11, n = 5, wv = $clog2( r**n ), wd = $clog2(n+1) )

( output logic [wv-1:0] val,

output logic [wd-1:0] nd,

input uwire [7:0] str [n-1:0] );

uwire [wv-1:0] vali[n:0];

uwire is_digit[n:0];

uwire [wd-1:0] ndi[n:0];

assign is_digit[n] = 0;

assign ndi[n] = 0;

assign vali[n] = 0;

assign nd = ndi[0];

assign val = vali[0];

localparam int wcv = $clog2(r);

for ( genvar i=n-1; i>=0; i-- ) begin

// Find Value of Digit i

uwire [wcv-1:0] vald;

atoi1 #(r,wcv) a( vald, is_digit[i], str[i] );

```

```

// Multiply (scale) the accumulated sum.

uwire [wv-1:0] valns;

mult_by_c #( .w_in(wv), .c(r), .w_out(wv) ) mc( valns, vali[i+1] );

```

```

// Update accumulated value.

assign vali[i] = is_digit[i] ? valns + vald : 0;

```

```

// Update number of digits.

assign ndi[i] = !is_digit[i] ? 0 : is_digit[i+1] ? ndi[i+1] : i + 1;

```

end endmodule

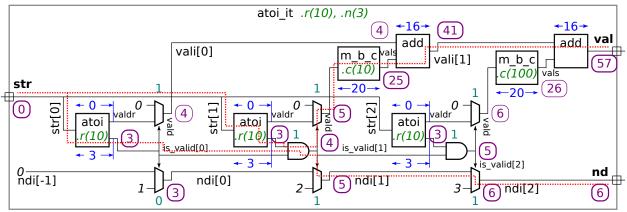

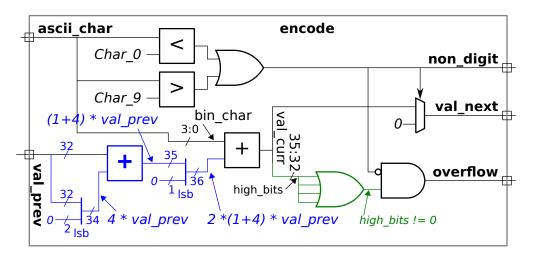

Problem 3: [20 pts] Illustrated below is the hardware for one of the atoi modules from Homework 3. The delays for the add, atoi1, and mult\_by\_c modules are shown in blue. For atoi the delay of the value (valdr) output is zero and the delay of the is\_digit (lower) output is 3.

(a) Based on the illustrated delays and using the simple model find the delay at each output, val and nd, and show the critical path to each.

Use the simple model and indicated delays to find the delay at outputs val and nd.

Show the critical path to both val and nd.

Take into account constant values.

(b) Modify the design to reduce the delay at val by moving multiplexors. The modification is simple though will increase cost. Show your modification either on the diagram or in the Verilog code below.

Modify to reduce the delay at val by moving multiplexors.

Do not change what the module does.

```

module atoi it

#( int r = 11, n = 5, wv = $clog2( r**n ), wd = $clog2(n+1) )

( output logic [wv-1:0] val, output logic [wd-1:0] nd,

input uwire [7:0] str [n-1:0] );

uwire [wv-1:0] vali[n-1:-1];

uwire is_valid[n-1:-1];

uwire [wd-1:0] ndi[n-1:-1];

assign is_valid[-1] = 1;

assign ndi[-1] = 0;

assign vali[-1] = 0;

assign nd = ndi[n-1];

assign val = vali[n-1];

localparam int wcv = $clog2(r);

for ( genvar i=0; i<n; i++ ) begin</pre>

uwire [wcv-1:0] valdr;

uwire is_digit;

atoi1 #(r,wcv) a( valdr, is_digit, str[i] ); // Find Value of Digit i

// Determine if this digit continues a sequence of valid digits.

11

assign is_valid[i] = is_digit && is_valid[i-1];

// Replace value with zero if str[i] is not a digit, or if the

// string of valid digits has already ended.

11

uwire [wcv-1:0] vald = is_valid[i] ? valdr : 0;

// Multiply (scale) the digit value based on its position in the number.

11

uwire [wv-1:0] vals;

mult_by_c #( .w_in(wcv), .c(r**i), .w_out(wv) ) mc( vals, vald );

// Add the scaled digit to the value accumulated so far.

11

add #(wv) a1( vali[i], vali[i-1], vals );

// Update the number of digits so far.

11

assign ndi[i] = is_valid[i] ? i+1 : ndi[i-1];

end

```

```

endmodule

```

Problem 4: [12 pts] Answer each question below.

(a) The module below will not compile because of the way the module connections are declared. Fix the problem by changing the declarations.

Change declaration to fix problem.

```

module yucx2

#( int w = 5 )

( output uwire [w-1:0] x,

input uwire [1:0] s,

input uwire [w-1:0] a0, a1 );

always_comb begin

x = a0;

if ( s != 0 ) x = a1;

end

```

endmodule

(b) The mv output of findmax is supposed to be set to the value of the largest of the three inputs. Assuming it compiles and simulates, it still won't work. Identify the problem.

Why won't mv be set to the maximum of a0, a1, a2?

Provide an example that illustrates the incorrect behavior.

```

module findmax

#( int w = 5 )

( output logic [w-1:0] mv,

input uwire [w-1:0] a0, a1, a2 );

initial mv = 0;

always_comb if ( mv < a0 ) mv = a0;

always_comb if ( mv < a1 ) mv = a1;

always_comb if ( mv < a2 ) mv = a2;</pre>

```

endmodule

Staple This Side

Problem 5: [12 pts] Answer each question below.

(a) Type logic is an example of a four-state type. Name those four states and describe what the non-numeric ones are used for.

Name the four logic states.

Describe what the non-numeric ones signify.

(b) Most synthesis programs will not synthesize a module that includes a delay, such as the one below. Why not?

```

module madd

#( int w )

( output logic [w-1:0] w,

input uwire [w-1:0] a, b, c );

always_comb begin

w = a * b;

#5; // Allow enough time for multiplication to finish.

w = w + a;

end

endmodule

```

Why isn't a delay synthesizeable?

Name \_

Formatted For Two-Sided Printing

# Digital Design using HDLs LSU EE 4755 Final Examination

Friday, 9 December 2022 15:00-17:00 CST

- Problem 1 \_\_\_\_\_ (20 pts)

- Problem 2 \_\_\_\_\_ (20 pts)

- Problem 3 \_\_\_\_\_ (15 pts)

- Problem 4 \_\_\_\_\_ (20 pts)

- Problem 5 \_\_\_\_\_ (25 pts)

Exam Total \_\_\_\_\_ (100 pts)

Alias

Good Luck!

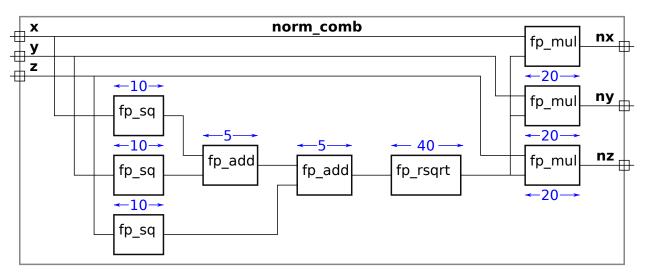

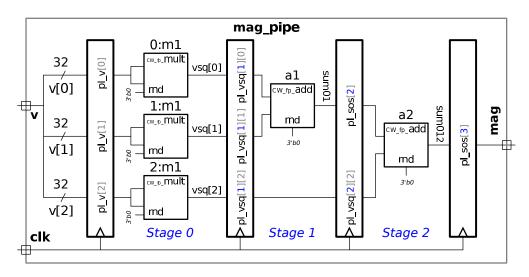

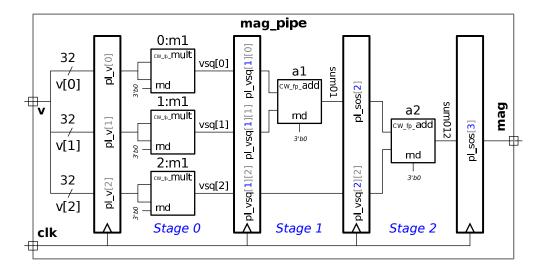

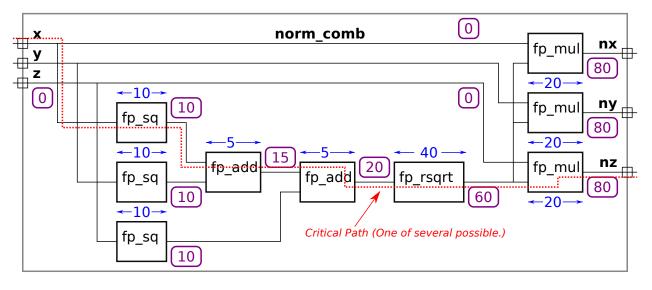

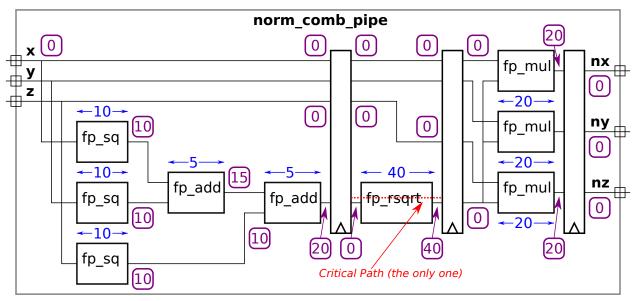

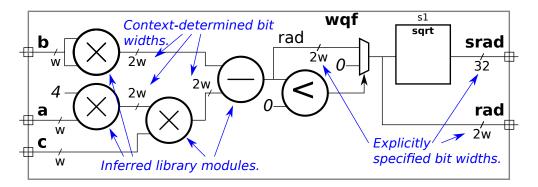

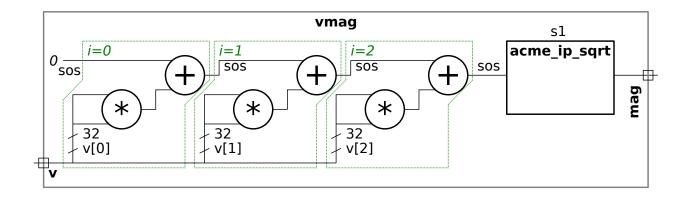

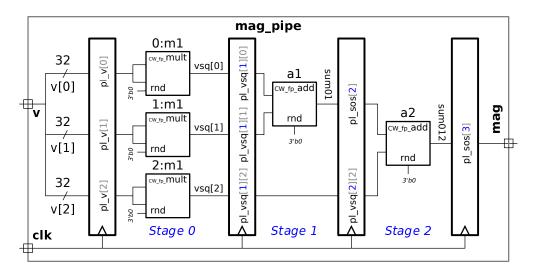

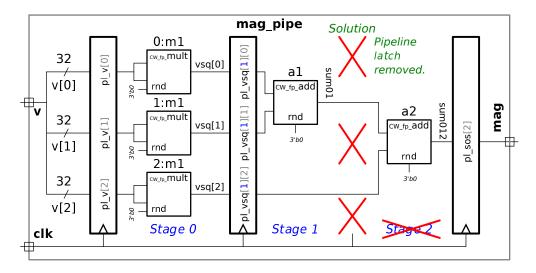

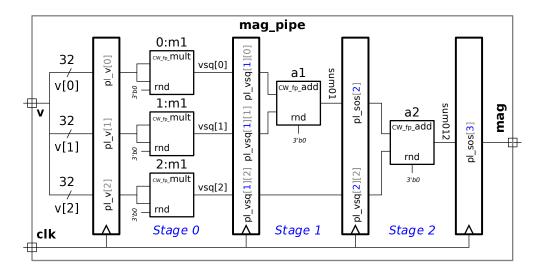

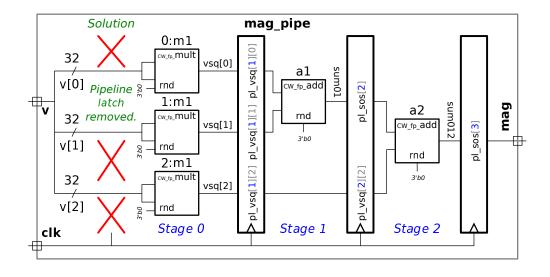

Problem 1: [20 pts] Module norm\_comb, below, computes the normal of a vector using floating-point arithmetic units from a library. The delay through each unit in nanoseconds is shown in the diagram.

(a) Compute the latency and throughput  $norm\_comb$  given the timings shown in the diagram.

Compute the arrival time (delay) at each module output.

Show the critical path.

The latency of this module is:

The throughput of this module is:

(b) Draw a diagram of a pipelined implementation of the norm module. The goal is to maximize throughput first then minimize latency **given the delays shown in the diagram from part a**. Give some thought as to what arithmetic units go in what stage. Show the latency and throughput of your pipelined implementation.

Draw a diagram (not Verilog) of a pipelined version of this **norm** module. Be sure to show pipeline latches.

For the given delays: Maximize throughput.  $\hfill Avoid a hasty solution that has a higher latency than is necessary.$

The latency of this pipelined implementation is:

The throughput of this pipelined implementation is:

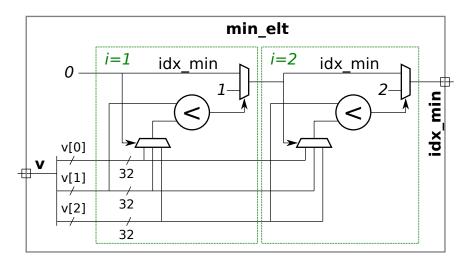

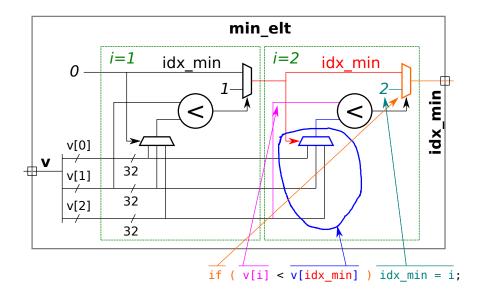

Problem 2: [20 pts] Incomplete module norm\_comb\_n is a version of the norm module from the previous problem, now written for vectors of any length, not just 3. (Output  $u_i = n_i \left(\sum_{j=0}^{n-1} v_j^2\right)^{-\frac{1}{2}}$ .) It makes use of module norm\_sos to compute the sum  $\sum_{j=0}^{n-1} v_j^2$ . (That is,  $v_0^2 + v_1^2 + \cdots + v_{n-1}^2$ .) Complete the modules so that they compute their output combinationally. Use a recursive implementation for norm\_sos and use generate loops for the needed code in norm\_comb\_n.

Complete norm\_comb\_n so that it computes u in part by using norm\_sos. Use a generate loop. Use fp\_mul, don't use arithmetic operators.

```

module norm_comb_n #( int w = 32, int n = 8 )

( output uwire [w-1:0] u[n], input uwire [w-1:0] v[n] );

uwire [w-1:0] sos; // Sum Of Squares

norm_sos #(w,n) ns( sos, v ); // This part is correct, don't modify it.

uwire [w-1:0] rmag, rs_in;

fp_rsqrt r( rmag, rs_in ); // [] Rename rs_in, or connect it to something.

// [] Compute u[0] = v[0] * rmag; u[1] = v[1] * rmag; ...

```

#### endmodule

Complete norm\_sos so that it computes  $\sum_{j=0}^{n-1} v_j^2$ . Describe the module recursively. Use fp\_sq and fp\_add, do not use arithmetic operators. module norm sos #( int w = 32, int n = 4 )

( output uwire [w-1:0] sos, input uwire [w-1:0] v[n-1:0] );

// [ ] Recursively compute: sos = v[0]^2 + v[1]^2 + ...

#### endmodule

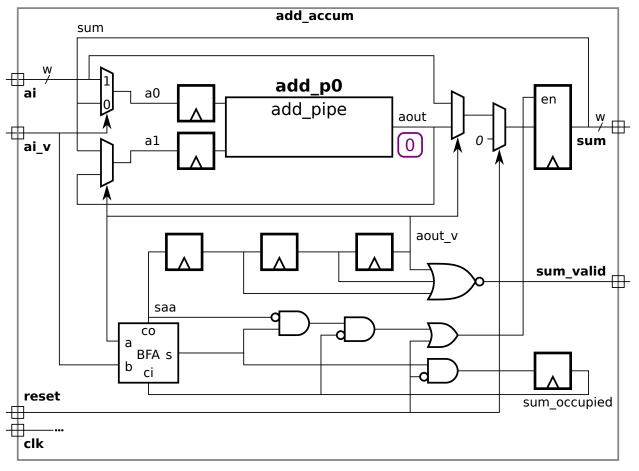

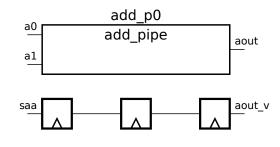

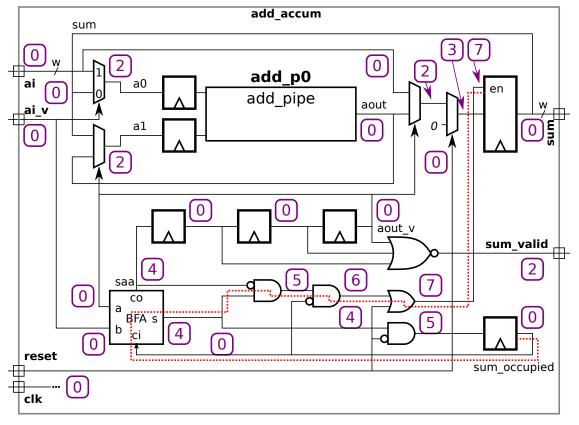

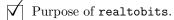

Problem 3: [15 pts] Appearing below is the inferred hardware from the pipelined add accumulate module covered in class. Based on the simple model, show the timing, including the critical path, and compute the cost. The BFA module is, of course, a binary full adder. If you don't remember its cost and delay, just work it out.

Show the timing (signal arrival time at each component output) and  $\Box$  the critical path.  $\Box$  Note that aout arrives at t = 0.

Compute the cost using the simple model. Do not include the cost of add\_pipe but include the cost of the BFA.

Pay attention to bit widths.

Problem 4: [20 pts] Appearing below are simplified solutions to Homework 4.

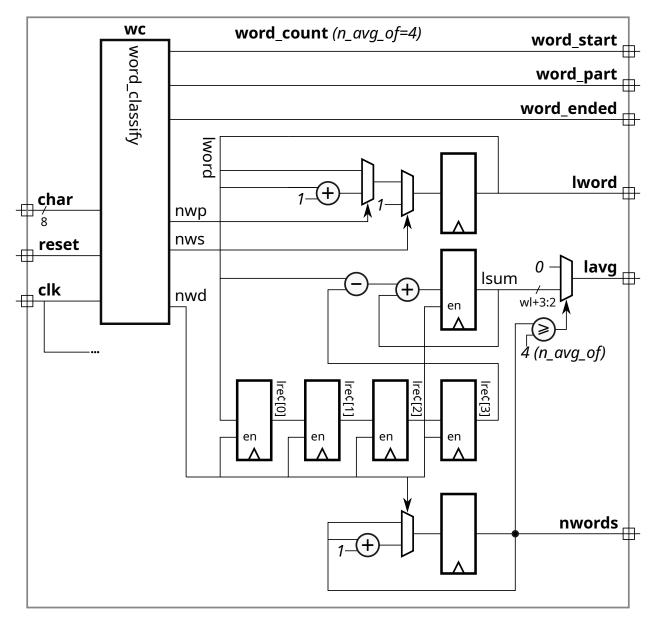

(a) Below is a simplified version of the "official" solution. (Reset hardware is not shown, ignore its absence. Some object names shortened.) Show the hardware that will be inferred for this module when instantiated with  $n_avg_of=4$ . (Some of the hardware will be similar to the  $r_avg2$  module from the 2021 final exam.)

```

module word count

#( int wl = 5, wn = 6, n_avg_of = 10 )

( output logic word_start, word_part, word_ended,

output logic [wl-1:0] lword, lavg,

output logic [wn-1:0] nwords,

input uwire [7:0] char,

input uwire reset, clk );

uwire nws, nwp, nwd;

word_classify wc( word_start, word_part, word_ended,

nws, nwp, nwd, char, clk, reset );

logic [wl-1:0] lrecent[n_avg_of]; // len_recent

logic [wl+$clog2(n_avg_of):0] lsum; // len_sum

assign lavg = nwords >= n_avg_of ? lsum / n_avg_of : 0;

always_ff @ ( posedge clk ) begin

lword <= nws ? 1 : nwp ? lword+1 : lword;</pre>

nwords <= nwd ? nwords + 1 : nwords;</pre>

end

// Plan A Code (Referred to in next subproblem.)

always_ff @ ( posedge clk ) if ( nwd ) begin

lsum += lword - lrecent[n_avg_of-1];

for ( int i=n_avg_of-1; i>0; i-- ) lrecent[i] = lrecent[i-1];

lrecent[0] = lword;

end

endmodule

```

Show inferred hardware for n\_avg\_of=4.

Show word\_classify as a box, don't attempt to show its contents.

Staple This Side

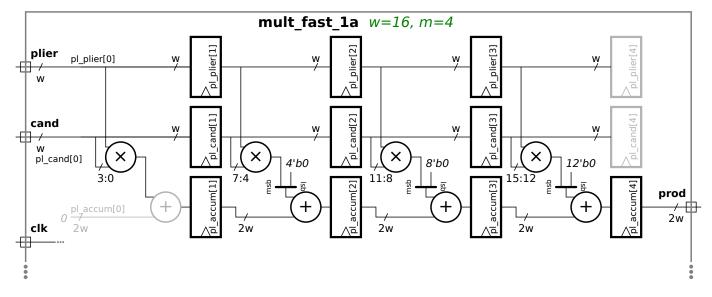

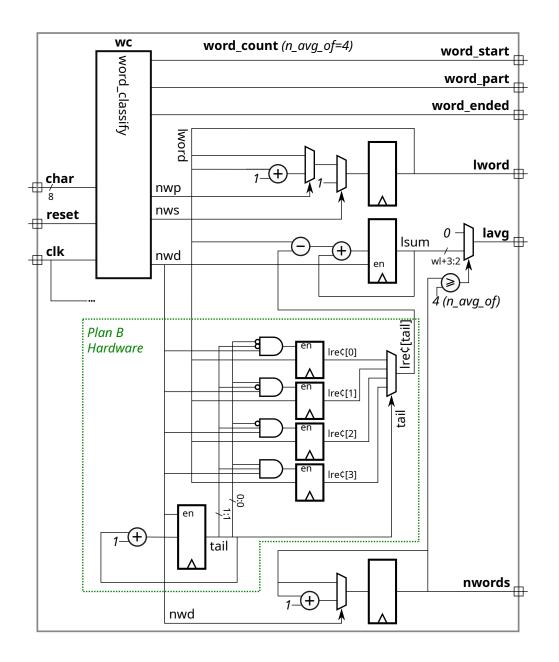

(b) The word\_count\_plan\_b module below uses a different approach to keeping track of lsum. The only difference is the hardware under the Plan B Code comment. This version avoids a loop! That's great, right? Show the hardware that will be inferred for the Plan B Code for  $n_avg_of = 4$  and indicate impact on cost and performance.

```

module word_count_plan_b

#( int wl = 5, wn = 6, n_avg_of = 10 )

( output logic word_start, word_part, word_ended,

output logic [wl-1:0] lword, lavg,

output logic [wn-1:0] nwords,

input uwire [7:0] char,

input uwire reset, clk );

uwire nws, nwp, nwd;

word_classify wc( word_start, word_part, word_ended,

nws, nwp, nwd, char, clk, reset );

logic [wl-1:0] lrecent[n_avg_of];

logic [wl+$clog2(n_avg_of):0] lsum;

logic [$clog2(n_avg_of):0] tail;

assign lavg = nwords >= n_avg_of ? lsum / n_avg_of : 0;

always_ff @ ( posedge clk ) begin

lword <= nws ? 1 : nwp ? lword+1 : lword;</pre>

nwords <= nwd ? nwords + 1 : nwords;</pre>

end

// Plan B Code

always_ff @ ( posedge clk ) if ( nwd ) begin

lsum += lword - lrecent[tail];

lrecent[tail] = lword;

tail = tail == n_avg_of - 1 ? 0 : tail + 1;

end

```

```

endmodule

```

Describe impact on cost of Plan B compared to Plan A.

Describe impact on performance of Plan B compared to Plan A.

Show inferred hardware for Plan B Code. (No need to show hardware for code above the Plan B Code comment.)

Consider using an enable (en) signal on the registers to simplify the hardware.

Problem 5: [25 pts] Answer each question below.

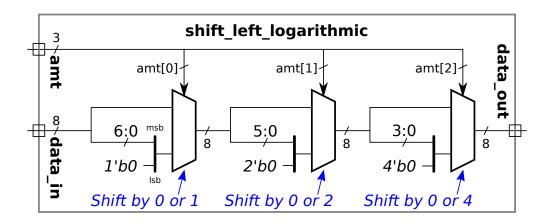

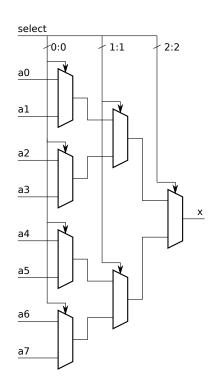

(a) Show a sketch of the hardware for an 8-bit left shift module, using the logarithmic approach presented in class.

| Show hardware for 8-bit left shift module. | Include the | 3-bit shift amount input, | the 8-bit data |

|--------------------------------------------|-------------|---------------------------|----------------|

| input and 8-bit data output.               |             |                           |                |

(b) Provide the following delays based on the simple model.

What is the delay for a w-bit ripple adder for  $\Box$  the LSB and  $\Box$  the MSB.

What is the delay for the sum of three *w*-bit values, say a + b + c, when computed using two ripple adders and accounting for cascading. Delay of the sum's  $\Box$  LSB and  $\Box$  MSB.

$\left(c\right)$  In the code fragment below there is an error in one of the last two lines.

```

module examples( input uwire [31:0] a, b );

localparam logic [31:0] la = a + b;

uwire logic [31:0] ua = a + b;

```

Which line above is incorrect? Why?

$\left(d\right)$  The code fragment below lacks declarations.

Declare objects **aa**, **ca**, and **fa** so that the code below is correct.

```

module examples( input uwire [31:0] a, b, input uwire clk );

```

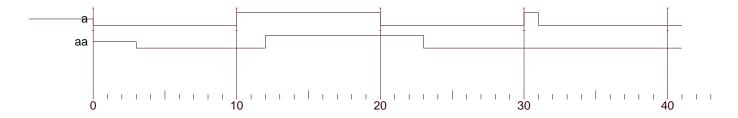

assign aa = a + b; always\_comb ca = a + b; always\_ff @( posedge clk ) fa = a + b;

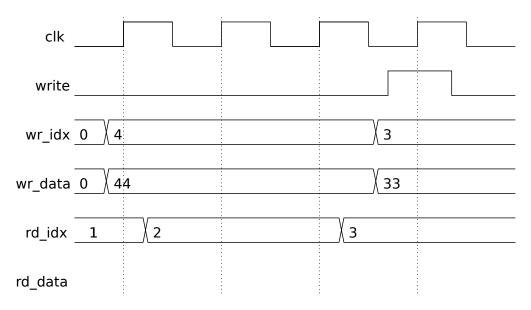

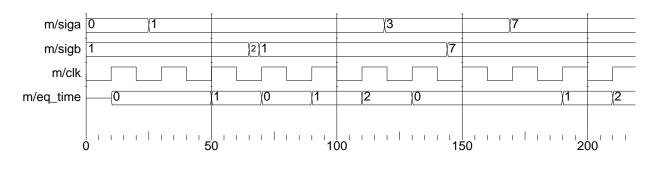

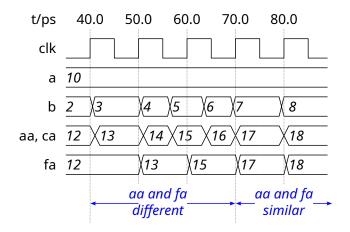

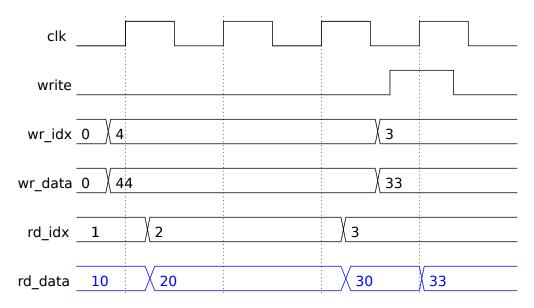

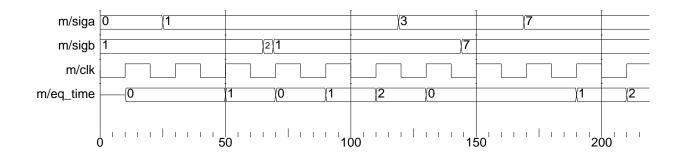

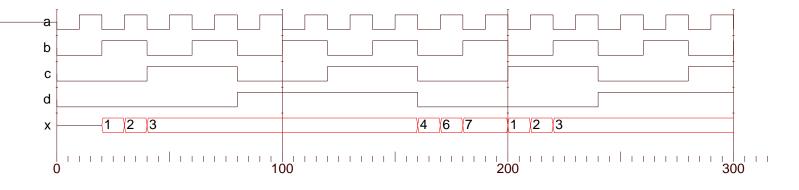

(e) Again consider the code above that assigns **aa**, **ca**, and **fa**. Draw a timing diagram that includes values of **a**, **b**, and **clk** for which at least one of the values **aa**, **ca**, and **fa** will at times differ from the others.

Draw a timing diagram showing how aa, ca, and fa won't all be the same all the time.

4 Fall 2021

Name

Formatted For 2-Sided Printing

# Digital Design Using HDLs LSU EE 4755 Midterm Examination

Wednesday, 27 October 2021, 11:30-12:20 CDT

- Problem 1 \_\_\_\_\_ (25 pts)

- Problem 2 \_\_\_\_\_ (30 pts)

- Problem 3 \_\_\_\_\_ (10 pts)

- Problem 4 \_\_\_\_\_ (10 pts)

- Problem 5 \_\_\_\_\_ (15 pts)

- Problem 6 (10 pts)

Exam Total \_\_\_\_\_ (100 pts)

Alias

Staple This Side

$\bigotimes V(\mathbf{r})$

$V(\text{mRNA}) \Rightarrow R_e < 1$

Good Luck!

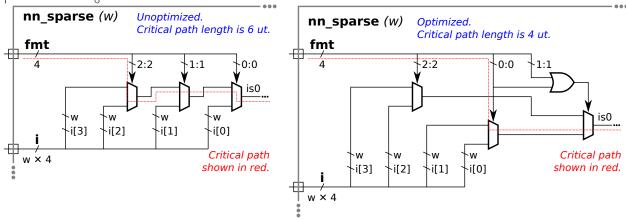

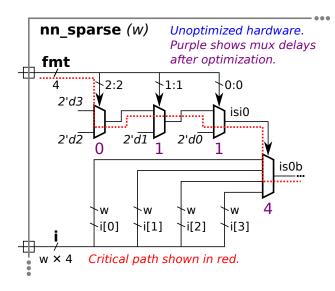

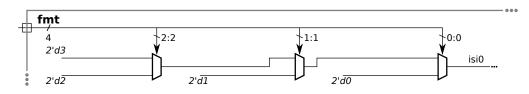

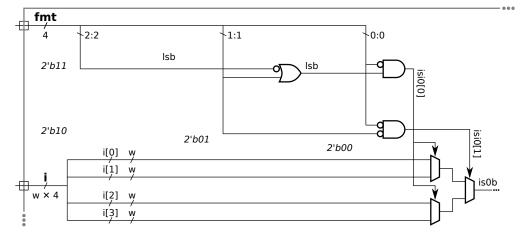

Problem 1: [25 pts] Appearing in this problem are two variations on hardware that selects one of four inputs, i, based on the position of the least-significant 1 in a 4-bit quantity, fmt. This is similar to the hardware needed in the solution to Homework 2, except that here i[3] can be selected.

```

module nn_sparse #( int w = 20 )

( output logic [w-1:0] o, input uwire [w-1:0] i[4], input uwire [3:0] fmt );

```

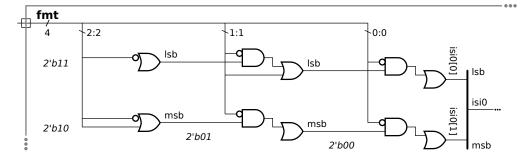

(a) Show the hardware that will be inferred for is0 and show that hardware after optimization.

```

uwire [w-1:0] is0 = fmt[0] ? i[0] : fmt[1] ? i[1] : fmt[2] ? i[2] : i[3];

```

Show inferred hardware.

Show optimized hardware. Hardware can be re-arranged to reduce delay.

Use only basic logic gates and multiplexors.

(b) Compute the cost and delay of the optimized hardware for is0 in terms of w. (That's w, not its default value.)

In terms of w cost is:

In terms of w delay is:

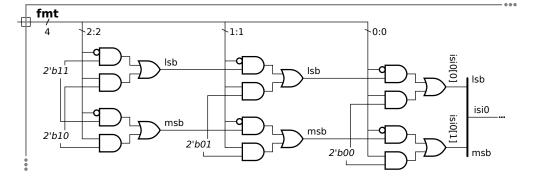

(c) Appearing below is an alternative design. Net isOb will have the same value as isO. Show the hardware below before and after optimization. For isiO do not show multiplexors after optimization. For isOb use two-input multiplexors (as many as needed).

```

uwire [1:0] isi0 = fmt[0] ? 0 : fmt[1] ? 1 : fmt[2] ? 2 : 3;

uwire [w-1:0] is0b = i[isi0];

```

Show inferred hardware.

Show optimized hardware, optimize to reduce delay.

Use basic logic gates and  $\square$  no muxen for isi0 and  $\square$  two-input muxen (plus other logic) for is0b.

(d) Compute the cost and delay of the optimized hardware (from the previous part) in terms of w. (That's w, not its default value.)

In terms of w cost is:

In terms of w delay is:

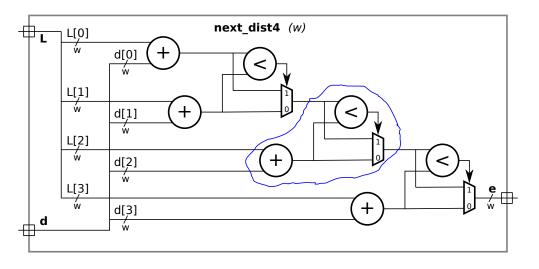

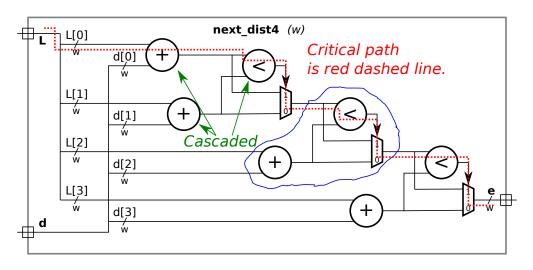

Problem 2: [30 pts] The next\_dist4 hardware illustrated below consists of several duplicated pieces of hardware, one of which is circled. Call the circled hardware an *ami* unit (for add-minimum).

(a) Compute the cost and delay of the module using the simple model, and show the critical path on the illustration. Assume that the adder and comparison units are based on ripple adders.

Cost in terms of w:

Show critical path.  $\Box$  Delay in terms of w:

Account for any cascading ripple units.

(b) Appearing below are two incomplete modules, one is an **ami** module the other is the **next\_dist4** module. Complete these modules to match the diagram using as many **ami** modules as needed. The **ami** module can use procedural or implicit structural code. The **next\_dist4** module must instantiate and use **ami** modules but can contain procedural or implicit structural code.

Complete the ami module so that it matches the circled hardware.

Complete the next\_dist4 module using as many ami modules as needed.

Don't forget to declare any intermediate objects that are used.

Noting that there are four adders and the width of each wire is w,  $\Box$  declare and use parameters appropriately.

module ami

endmodule

(c) Incomplete module next\_dist is a generalization of next\_dist4 to n elements per input. The module includes a generate loop. Use that loop to instantiate ami modules so that it performs the correct calculation. Keep the loop simple, don't try to fix the delay problem.

Complete module, taking advantage of the generate loop.

Be sure to instantiate ami modules, 🗌 connect the first ami correctly, 🗍 and don't leave e unconnected.

```

module next_dist #( int n = 20, w = 12 )

( output uwire [w-1:0] e,

input uwire [w-1:0] L[n], input uwire [w-1:0] d[n] );

localparam logic [w-1:0] mv = ~w'(0); // Can use as input to first ami.

uwire [w-1:0]

```

for ( genvar i=0; i<n; i++ ) begin</pre>

end

endmodule

$\mathbf{6}$

Problem 3: [10 pts] Consider the with\_assign module below.

## endmodule

(a) Why might the module confuse or annoy humans?

with\_assign could be confusing because:

(b) The module makes extra work for simulators too. Suppose that the input values to with\_assign, b and c, change at t = 10. About how many times will each line below execute in a worst-case scenario? The following sentence was not in the original exam: Use sensitivity lists to justify your answer.

About how many times does each line execute?  $\square$  Explain with sensitivity lists.

(c) Complete the sans\_assign routine below so that it does the same thing as with\_assign but is less confusing and less work for simulators.

Complete routine below. (Yes, it's easy but not trivial.)

end endmodule

Why does sans\_assign make less work for the simulator than with\_assign? Explain using sensitivity lists.

Problem 4: [10 pts] Appearing below is an ordinary multiplier, followed by a multiplier that is naïvely designed to take advantage of special cases (first operand is 0 or 1), followed by a module that instantiates both.

```

module mult #( int w = 32 )

( output logic [w-1:0] p, input uwire [w-1:0] a, b );

always_comb p = a * b;

endmodule

module mult_1a #( int w = 32 )

( output logic [w-1:0] p, input uwire [w-1:0] a, b );

always_comb begin

if ( a == 0 ) p = 0;

else if ( a == 1 ) p = b;

else p = a * b;

end

endmodule

module nm #( int w = 32, logic [w-1:0] c = 12 )

( output uwire [w-1:0] prods[4], input uwire [w-1:0] a[4], b[4] );

mult #(w)

m1 ( prods[0], a[0], b[0] );

mult #(w)

m2 ( prods[1], c,

b[1] );

mult_1a #(w)

ma1( prods[2], a[0], b[0] );

mult_1a \#(w)

ma2( prods[3], c,

b[1]);

endmodule

```

Explain why m1 will be faster (lower delay) than ma1, even when possible values of a[0] include 0, 1, and other values. Assume good synthesis programs.

How will the cost and performance of m2 and ma2 compare (to each other) using good synthesis programs? That is,  $\square$  which should be chosen when delay is the only concern and,  $\square$  which of the two should be chosen when cost is the only concern. The answer should not depend on any particular value of c.

Staple This Side

Problem 5: [15 pts] Answer the following questions about Verilog syntax and semantics.

(a) Appearing below are four variations on a multiplier with a constant input. Most have errors that would prevent them from compiling. For each indicate whether there is an error, and if so, what the error is and a minimal fix.

$\bigcirc$  correct or  $\bigcirc$  has the following error and fix: Module is module mult\_2a #( int w = 32, logic [w-1:0] a = 12 ) ( output uwire [w-1:0] p, input uwire [w-1:0] b ); if ( a == 0 ) p = 0;else if ( a == 1 ) p = b; p = a \* b;else endmodule Module is () correct or () has the following error and fix: module mult\_2b #( int w = 32, logic [w-1:0] a = 12 ) ( output uwire [w-1:0] p, input uwire [w-1:0] b ); always\_comb begin if ( a == 0 ) p = 0;else if (a == 1) p = b;else p = a \* b;end endmodule Module is  $\bigcirc$  correct or  $\bigcirc$  has the following error and fix: module mult\_2c #( int w = 32, logic [w-1:0] a = 12 ) ( output uwire [w-1:0] p, input uwire [w-1:0] b ); if (b == 0)p = 0;else if ( b == 1 ) p = a; else p = a \* b;endmodule Module is () correct or () has the following error and fix: module mult\_2d #( int w = 32, logic [w-1:0] a = 12 ) ( output uwire [w-1:0] p, input uwire [w-1:0] b );

> if ( a == 0 ) assign p = 0; else if ( a == 1 ) assign p = b; else assign p = a \* b;

endmodule

(b) Show the values of  ${\tt b}$  and  ${\tt c}$  where requested below.

```

module assortment;

logic [15:0] a;

logic [0:15] b;

logic [16:1] c;

initial begin

a = 16'h1234;

b = a;

c = a;

// Show value of b and c after line above executes:

#1; // Not really needed.

for ( int i=0; i<16; i++ ) b[i] = a[i];

// Show value of b after line above executes:

end

```

endmodule

Problem 6: [10 pts] Answer the following synthesis questions.

(a) Cadence Genus defines the following three synthesis steps: syn\_gen (generic), syn\_map (mapped, or technology mapping), and syn\_opt (optimized). Answer the following questions about technology mapping.

Explain what happens during technology mapping.

Even if optimization were done before technology mapping why is it important optimize after technology mapping?

(b) What is the big disadvantage of setting the delay target too low when performing synthesis? (The small disadvantage is that it takes a longer time to run.)

Disadvantage of setting delay target too low during synthesis:

Name \_

## Digital Design using HDLs LSU EE 4755 Final Examination

Wednesday, 8 December 2021 7:30 CST

Problem 1 \_\_\_\_\_ (30 pts)

- Problem 2 \_\_\_\_\_ (35 pts)

- Problem 3 \_\_\_\_\_ (15 pts)

- Problem 4 \_\_\_\_\_ (20 pts)

Exam Total \_\_\_\_\_ (100 pts)

Alias

Good Luck!

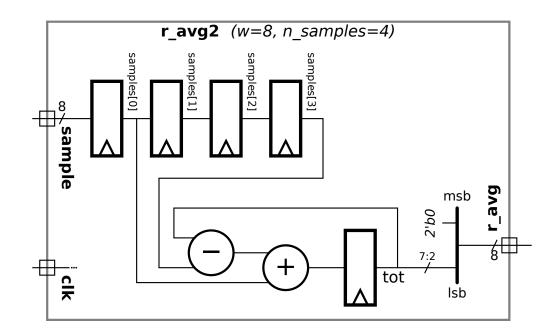

Problem 1: [30 pts] For the modules in this problem input sample holds a new value each cycle, and output r\_avg holds the average of the last n\_samples inputs. (Ignore the fact that the module needs but lacks a reset.)

(a) For the module below show the hardware that will be inferred when instantiated with default parameters. Be sure to optimize for the default value of n\_samples.

```

module ravg2 #( int w = 8, n_samples = 4 )

( output logic [w-1:0] r_avg,

input uwire [w-1:0] sample,

input uwire clk );

logic [w-1:0] samples[n_samples];

parameter int wm = $clog2( n_samples );

parameter int ws = w + wm;

logic [ws-1:0] tot;

always_ff @( posedge clk ) begin

samples[0] <= sample;</pre>

for ( int i=1; i<n_samples; i++ ) samples[i] <= samples[i-1];</pre>

tot <= tot - samples[n_samples-1] + samples[0];</pre>

end

```

```

always_comb r_avg = tot / n_samples;

```

endmodule

Show hardware for the module above using default parameter values.

Optimize for these parameter values.

Staple This Side

(b) The module to the right is similar to ravg2 except that it has three arithmetic unit instantiations: an adder, a subtractor, and a divide-by-constant unit. Modify ravg3 so that it uses these modules. For full credit connect them so that the critical path passes through at most one module per cycle. In a correct solution r\_avg will arrive at the output of ravg3 later than it would in module ravg2.

Modify ravg3 so that it uses the three arithmetic units.

- For full credit, the critical path can go through at most one arithmetic unit per cycle.

- The connections to the arithmetic units can be changed (say from **aa1** to something else).

- Do not add unnecessary cost or delay.

```

module ravg3 #( int w = 8, n_samples = 4 )

( output logic [w-1:0] r_avg,

input uwire [w-1:0] sample,

input uwire clk );

logic [w-1:0] samples[n_samples];

parameter int wm = $clog2( n_samples );

parameter int ws = w + wm;

logic [ws-1:0] tot;

always_ff @( posedge clk ) begin

samples[0] <= sample;

for ( int i=1; i<n_samples; i++ ) samples[i] <= samples[i-1];

tot <= tot - samples[n_samples-1] + samples[0]; // Modify or eliminate this line.</pre>

```

#### end

```

always_comb r_avg = tot / n_samples; // Modify or eliminate this line.

uwire [ws-1:0] sum, diff;

uwire [ws-1:0] aa1, aa2, da1;

```

uwire [w-1:0] quot;

uwire [w-1:0] sa1, sa2;

| <pre>our_adder #(ws,ws)</pre>           | add1( sum,             | aa1,   | aa2 ); |

|-----------------------------------------|------------------------|--------|--------|

| our_sub #(ws,w)                         | <pre>sub2( diff,</pre> | sa1,   | sa2 ); |

| <pre>our_div_by #(w,ws,n_samples)</pre> | div3( quot,            | da1 ); |        |

### endmodule

Staple This Side

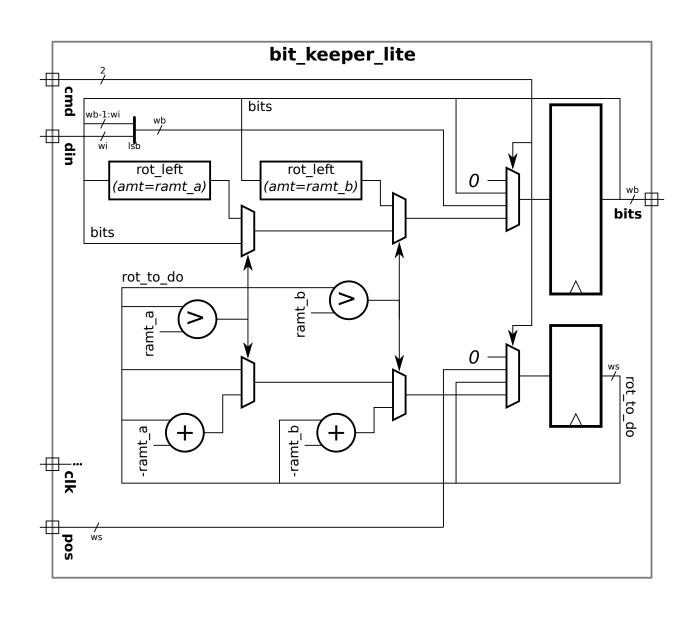

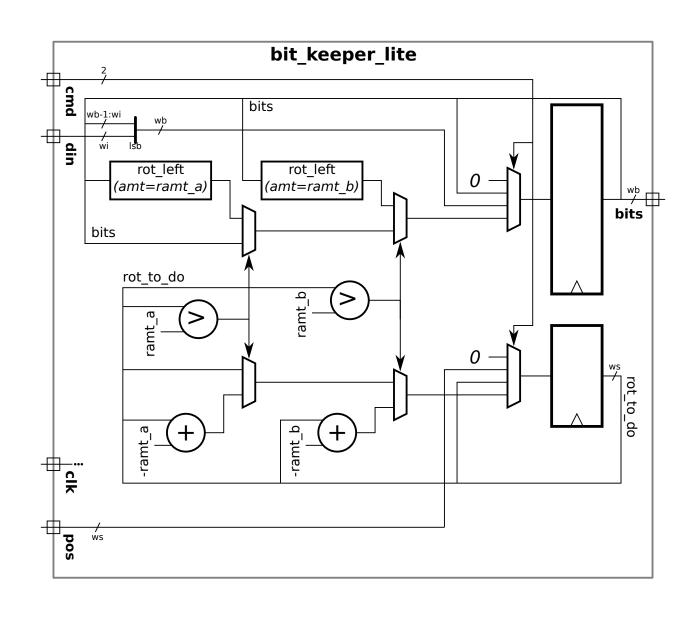

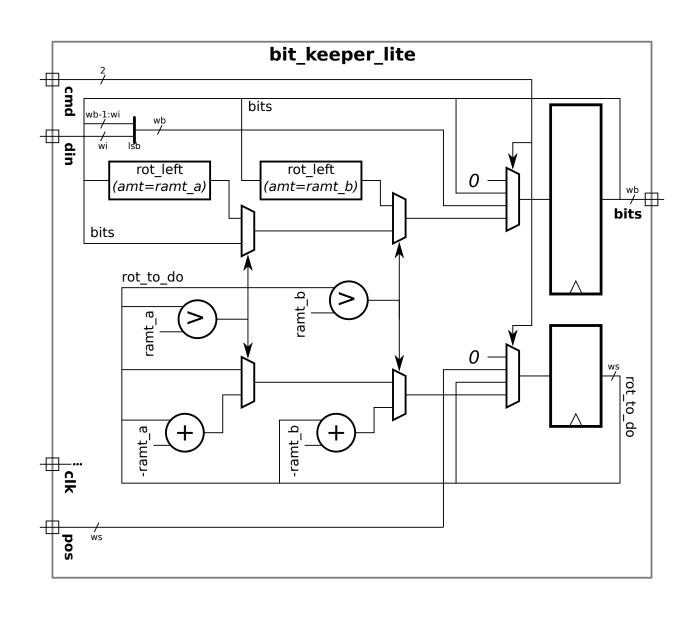

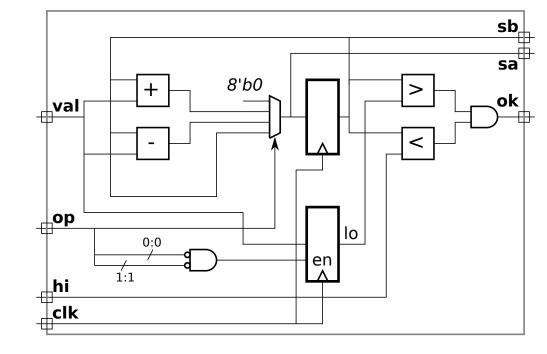

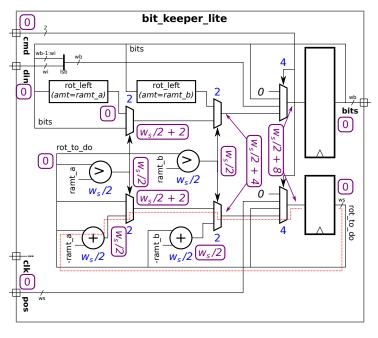

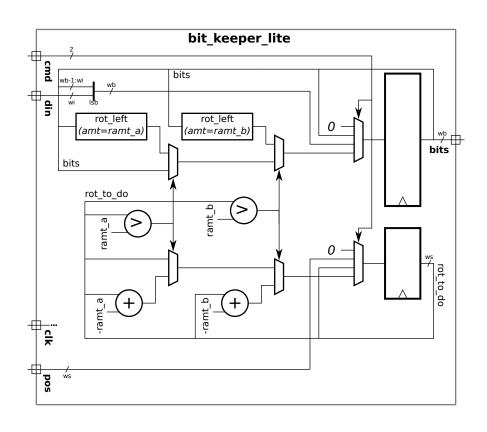

Problem 2: [35 pts] Appearing below is a Verilog description of a lower-cost version of the bit\_keeper module from Homework 4 and a diagram of the hardware.

```

typedef enum { Cmd_Reset=0, Cmd_Rot_To=1, Cmd_Write=2, Cmd_Nop=3, Cmd_SIZE } Command;

module rot left #( int w = 10, amt = 1 )

( output uwire [w-1:0] r, input uwire [w-1:0] a);

assign r = \{ a[w-amt-1:0], a[w-1:w-amt] \};

endmodule

module bit_keeper_lite #( int wb = 64, wi = 8, ws = $clog2(wb) )

( output logic [wb-1:0] bits,

output uwire ready,

input uwire [1:0] cmd,

input uwire [wi-1:0] din,

input uwire [ws-1:0] pos,

input uwire clk );

localparam int ramt_a = 1;

// Specify Rotation Amounts

localparam int ramt_b = 1 << ( ws >> 1 );

uwire [wb-1:0] ra, rb;

rot_left #(wb,ramt_a) rl1(ra,bits);

rot_left #(wb,ramt_b) rl8(rb,bits);

logic [ws-1:0] rot_to_do;

// Remaining amount of rotation to do.

assign ready = rot_to_do == 0;

always_ff @( posedge clk ) case ( cmd )

Cmd_Reset: begin bits = 0; rot_to_do = 0; end

Cmd_Rot_To: rot_to_do = pos; // Initialize rotation. Rotate during Nop.

Cmd_Write: bits[wi-1:0] = din;

Cmd_Nop:

// Continue Executing a Cmd_Rot_To

if ( rot_to_do >= ramt_b ) begin

// Use output of larger rot module.

bits = rb;

rot_to_do -= ramt_b;

// Decrement remaining rot amt.

end else if ( rot_to_do >= ramt_a ) begin

bits = ra;

// Use output of smaller rot module.

rot_to_do -= ramt_a; // Decrement remaining rot amt.

end

endcase

endmodule

```

(a) Find the cost and delay of the illustrated hardware using the simple model. Take into account the presence of constants. For the addition and comparison units assume a ripple implementation. Show any assumptions made. (See the next part before solving this one.)

Show cost in terms of  $w_b$ ,  $w_i$ , and  $w_s$ .  $\Box$  Take into account constants.

Show delays and arrival times on the diagram, and  $\square$  highlight the critical path. These should be in terms of  $w_b$ ,  $w_i$ , and  $w_s$ .

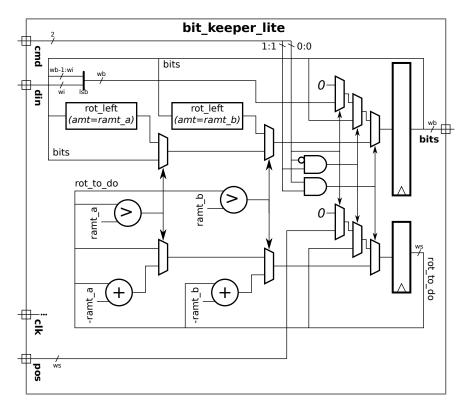

(b) In class we assume that a four-input mux is implemented using a reduction tree of 3 two-input muxen. For the illustrated hardware that would result in a longer critical path than is necessary. Modify the diagram on the right to show a better way of implementing the four-input multiplexors.

Replace four-input multiplexors with two-input muxen connected to reduce critical path.

(c) Notice that care was taken to ensure that ramt\_b is a power of 2. Explain how the fact that ramt\_b is a power of two reduces the cost of the adder and comparison unit operating on ramb\_b. Also explain how a power-of-2 ramb\_b can reduce the cost of the other adder and comparison unit, if the synthesis program is clever enough. *Hint: Consider the binary representation of* rot\_to\_do.

Since ramt\_b is a power of 2 the adder and comparison unit connected to ramt\_b are lower cost because:

Since ramt\_b is a power of 2 the adder and comparison unit connected to ramt\_a (yes, a) are lower cost because:

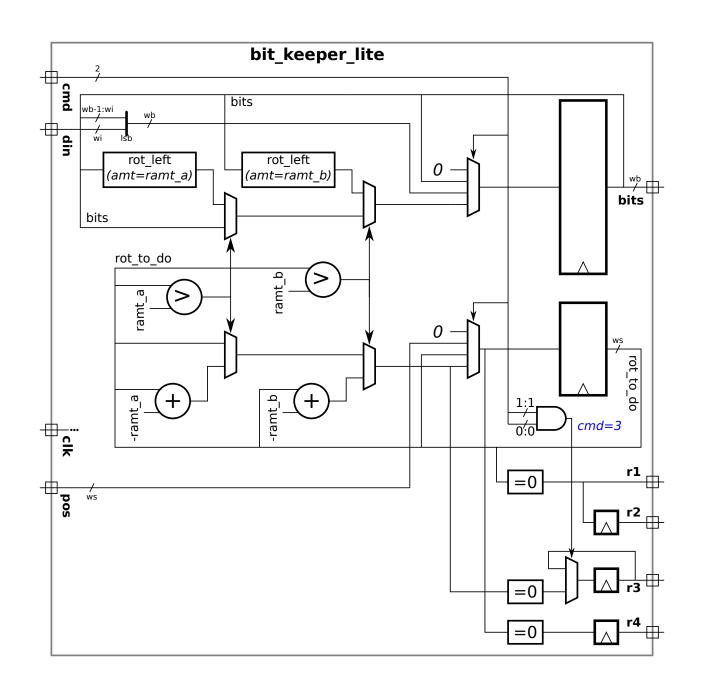

(d) Appearing below is a version of  $bit_keeper_lite$  with four ready outputs, r1, r2, r3, and r4. On the diagram add hardware that will be synthesized for each.

```

module bit keeper lite #( int wb = 64, wi = 8, ws = $clog2(wb) )

( output logic [wb-1:0] bits, output uwire r1, output logic r2, r3, r4,

input uwire [1:0] cmd,

input uwire [wi-1:0] din,

input uwire [ws-1:0] pos,

input uwire clk );

localparam int ramt_a = 1;

localparam int ramt_b = 1 << ( ws >> 1 );

uwire [wb-1:0] ra, rb;

rot_left #(wb,ramt_a) rl1(ra,bits);

rot_left #(wb,ramt_b) rl8(rb,bits);

logic [ws-1:0] rot_to_do;

assign r1 = rot_to_do == 0;

// [ ] Show hardware for r1.

always_ff @( posedge clk ) begin

r2 = rot_to_do == 0;

// [ ] Show hardware for r2.

case ( cmd )

Cmd_Reset: begin bits = 0; rot_to_do = 0; end

Cmd_Rot_To: rot_to_do = pos;

Cmd_Write: bits[wi-1:0] = din;

Cmd_Nop: begin

if ( rot_to_do >= ramt_b ) begin

bits = rb;

rot_to_do -= ramt_b;

end else if ( rot_to_do >= ramt_a ) begin

bits = ra;

rot_to_do -= ramt_a;

end

r3 = rot_to_do == 0;

// [ ] Show hardware for r3.

end

endcase

r4 = rot_to_do == 0;

// [ ] Show hardware for r4.

end

endmodule

```

Show hardware that will be synthesized for  $\tt r1, r2, r3,$  and  $\tt r4.$

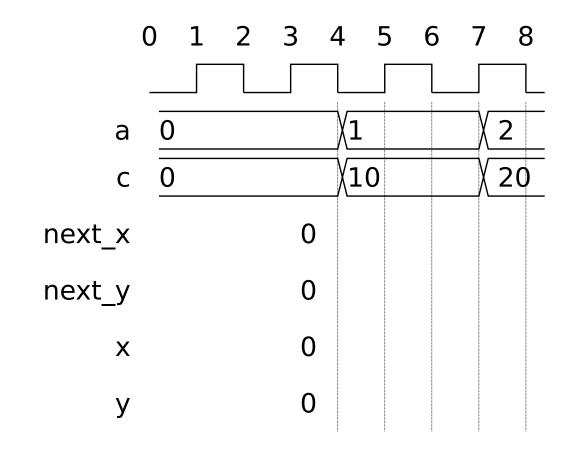

Problem 3: [15 pts] Consider the modules below.

```

module ba

( output logic [15:0] next_x, next_y, x, y,

input uwire [15:0] a, c, input uwire clk );

always_ff @( posedge clk ) x = next_x;

assign next_x = a;

assign next_y = x + c;

always_ff @( posedge clk ) y = next_y;

endmodule

module test_ba;

uwire [15:0] x, y, next_x, next_y;

logic [15:0] a, c;

logic clk;

ba ba1( next_x, next_y, x, y, a, c, clk );

initial begin

// t = 0

clk = 0;

a = 0; c = 0;

#1; // t = 1

clk = 1;

#1; // t = 2

clk = 0;

#1; // t = 3

clk = 1;

#1; // t = 4

clk = 0; a <= 1; c <= 10; // Line t4

#1; // t = 5

clk = 1;

#1; // t = 6

clk = 0;

#1; // t = 7

clk = 1; a <= 2; c <= 20; // Line t7

#1; // t = 8

clk = 0;

end

```

```

endmodule

```

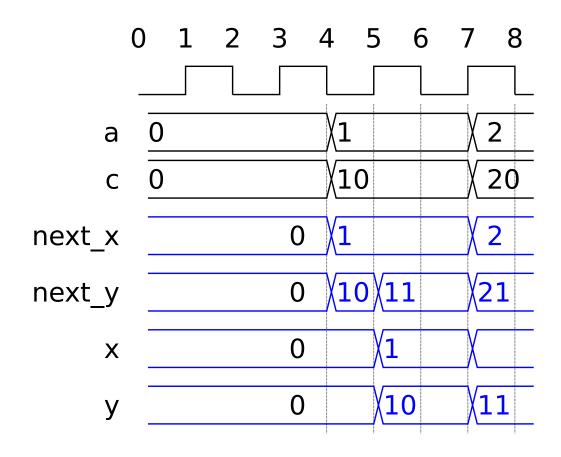

(a) Complete the timing diagram so that it shows the values of next\_x, next\_y, x, and y that would be produced with the modules above. *Note: In the original exam* test\\_ba *did not use non-blocking assignments to* a *and* c.

Complete timing diagram from t = 4 to t = 8.1.  $\square$  Note that there is a **negative** clock edge at t = 4.

(b) At t = 5 we can be sure that  $y=next_y$  will execute before  $next_y=x+c$ . Explain how this ordering is assured by the rules for the event queue.

Explain how event queue regions assure  $y=next_y$  executes before  $next_y=x+c$  at t=5.

(c) Notice that a and c are assigned using non-blocking assignments on Lines t4 and t7. Explain why the order of execution would be ambiguous at t = 7 if line t7 used blocking assignments: a=1; c=10;. Note: This question was not in the original exam.

Describe ambiguity (more than one possible execution order) if blocking assignments were used.

Would non-blocking assignments x <= next\_x and y <= next\_y remove the ambiguity?

Staple This Side

Problem 4: [20 pts] Answer each question below.

(a) The foolish  ${\tt sqrt}$  module below has several issues.

```

module sqrt #( int w = 16 )

( output logic [w-1:0] r, input uwire [w-1:0] a );

```

always\_comb begin

r = 0; while ( r \* r < a ) r++;</pre>

end

endmodule

Explain why, due to the Verilog rules for bit widths, the expression r \* r < a won't compute the intended result.

Why is the sqrt module likely not synthesizeable?

What would be the problem with the hardware if it were synthesizable?

(b) Consider the two division modules below. In the first **a2** is a parameter, in the second it is a module port. Use the **div\_demo** module for your answers to the questions below.

```

module our_div_by

#( int wq = 5, wd = 10, logic [wd-1:0] a2 = 4 )

( output uwire [wq-1:0] quot, input uwire [wd-1:0] a1 );

assign quot = a1/a2;

endmodule

```

### module our\_div

```

#( int wq = 5, wd = 10 )

( output uwire [wq-1:0] quot, input uwire [wd-1:0] a1, a2 );

// cadence inline

assign quot = a1/a2;

endmodule

```

```

module div_demo

```

```

#( int w = 21 )

( output uwire [w-1:0] d1, d2,

input uwire [w-1:0] x1, x2, x3, x4 );

```

```

localparam logic [w-1:0] y1 = 4755;

```

### endmodule

Show an instantiation of our\_div for which our\_div\_by could work.

Show an instantiation of  $\mathtt{our\_div}$  for which  $\mathtt{our\_div\_by}$  could not work.

Explain how the use of the cadence inline pragma in our\_div makes it possible to instantiate our\_div in places that otherwise might need our\_div\_by.

$\left(c\right)$  Answer the following questions about latency and throughput.

Define latency.

Define throughput.

Consider a sequential circuit (such as mult\_step from Homework 6) and a pipelined version of the sequential circuit (such as multi\_step\_pipe). Assume that both have the same clock frequency.

Remembering that the clock frequencies are the same, compared to the sequential version, does the pipelined version typically have

O lower latency,

O the same latency, or

O higher latency.

Explain.

| Compared to the seque        | ntial version, does the pipel     | ined version typically have      |          |

|------------------------------|-----------------------------------|----------------------------------|----------|

| $\bigcirc$ lower throughput, | $\bigcirc$ the same throughput, o | or $\bigcirc$ higher throughput. | Explain. |

**Ignoring the cost of registers**, compared to the sequential version, does the pipelined version typically have  $\bigcirc$  lower cost,  $\bigcirc$  the same cost, or  $\bigcirc$  higher cost.  $\square$  Explain.

$\leftarrow \ \rightarrow \ {\rm Fall} \ 2021 \qquad \leftarrow \ \rightarrow \ {\rm Final} \ {\rm Exam}$

5 Fall 2020

Name

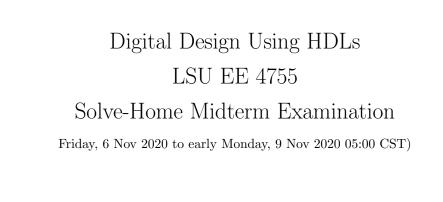

# Digital Design Using HDLs LSU EE 4755 Solve-Home Midterm Examination Friday, 6 Nov 2020 to early Monday, 9 Nov 2020 05:00 CST)

Work on this exam alone. Regular class resources, such as notes, papers, documentation, and code, can be used to find solutions. Outside material that covers the same topics, such as Verilog tutorials, digital logic design guides can also be used. Do not try to directly seek out solutions to any question here. That is, don't Web-search the text of a problem. Do not discuss this exam with classmates or anyone else, except questions or concerns about problems should be directed to Dr. Koppelman.

Warning: Unlike homework assignments collaboration is not allowed on exams. Suspected copying will be reported to the dean of students. The kind of copying on a homework assignment that would result in a comment like "See ee4755xx for grading comments" will be reported if it occurs on an exam. Please do not take advantage of pandemic-forced test conditions to cheat!

- Problem 1 \_\_\_\_\_ (20 pts)

- Problem 2 \_\_\_\_\_ (20 pts)

- Problem 3 \_\_\_\_\_ (20 pts)

- Problem 4 \_\_\_\_\_ (20 pts)

- Problem 5 \_\_\_\_\_ (20 pts)

Exam Total \_\_\_\_\_ (100 pts)

Good Luck!

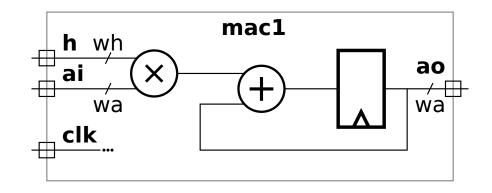

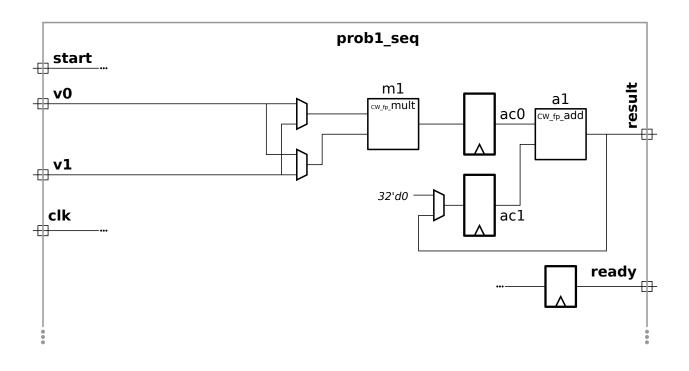

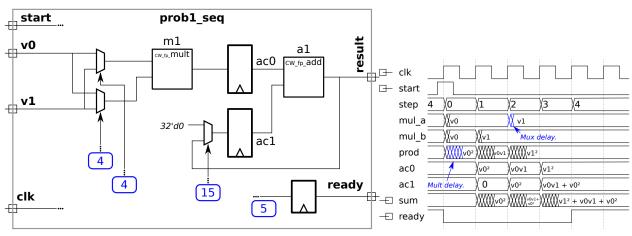

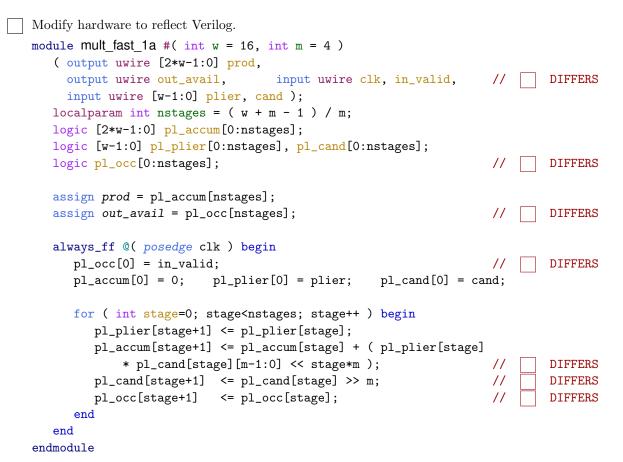

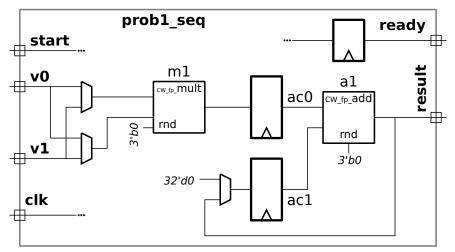

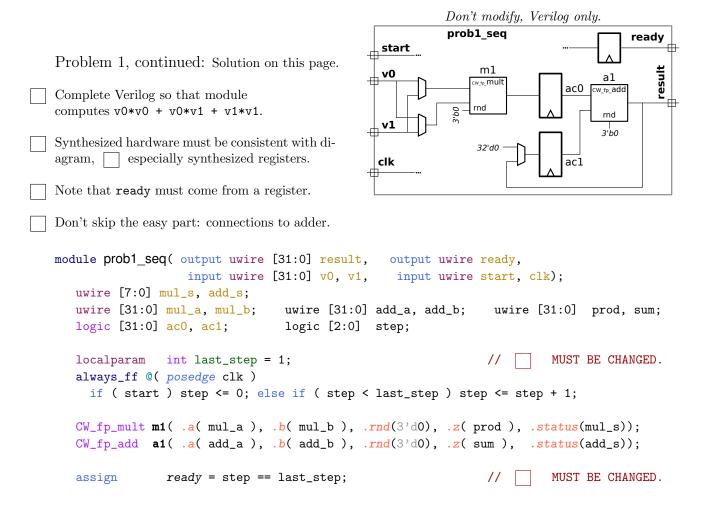

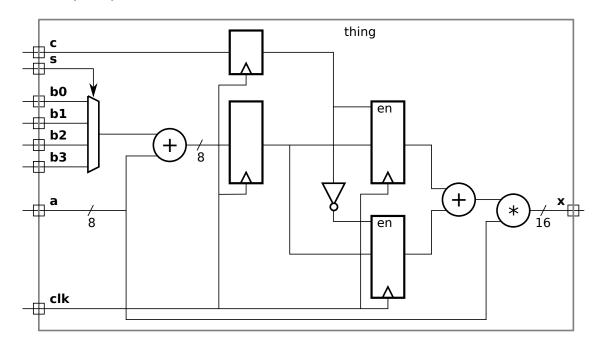

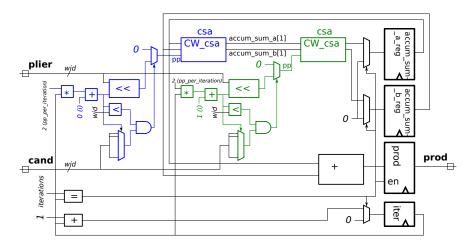

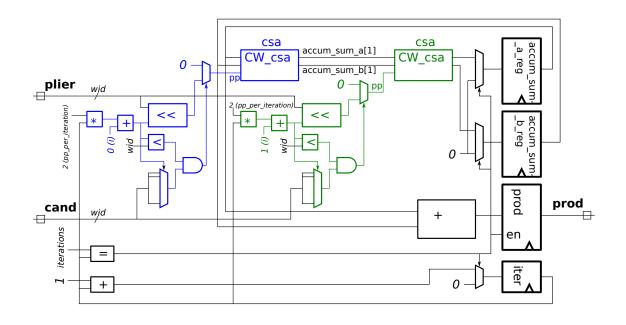

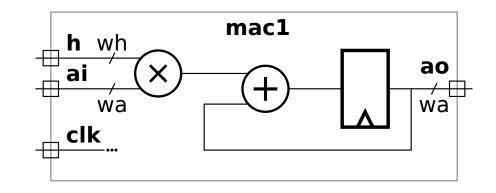

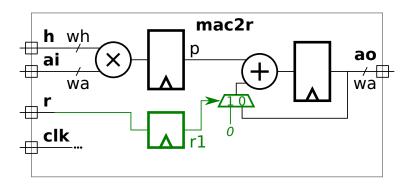

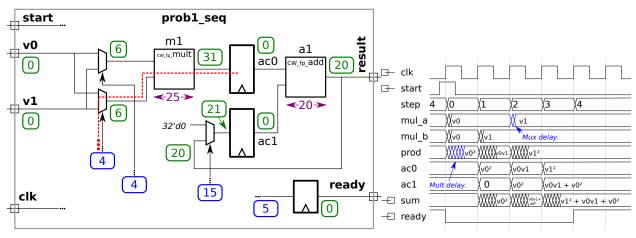

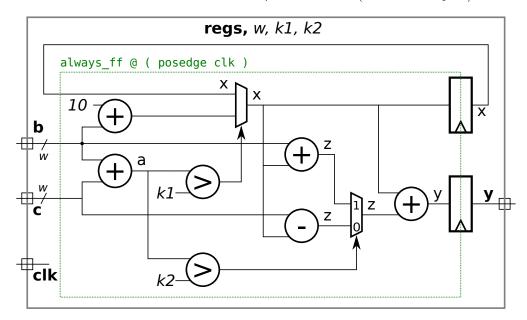

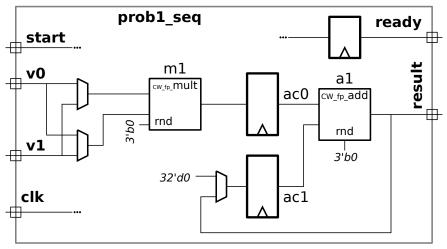

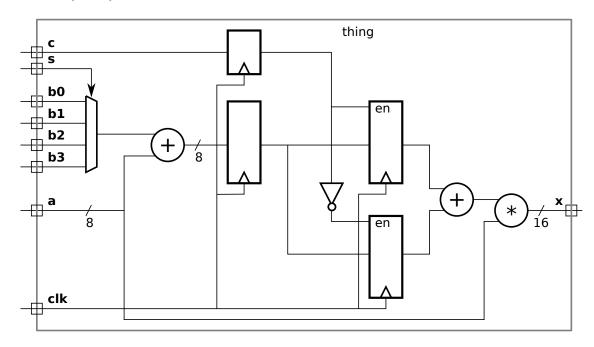

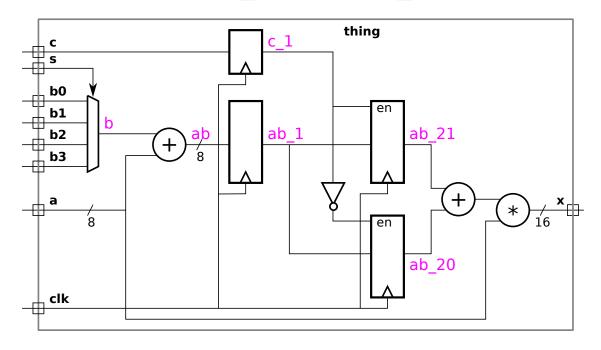

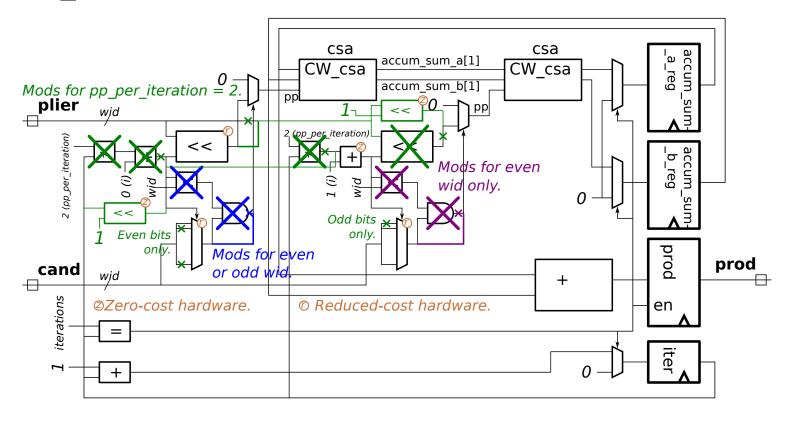

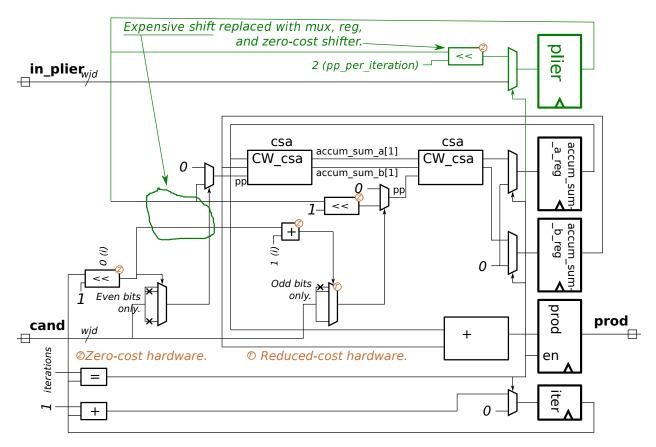

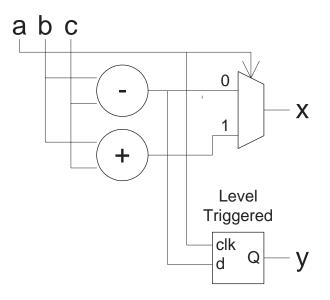

Problem 1: [20 pts] Appearing below are some variations on a multiply accumulate module.(a) Complete the Verilog code below so that it matches the illustration.

Complete the Verilog.

Use parameters for the bit widths wh and wa.

The registers inferred from the Verilog must match the diagram.

module mac1

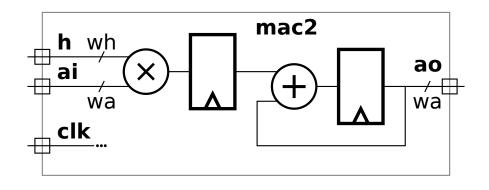

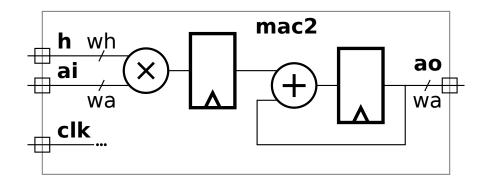

$\left(b\right)$  Complete the Verilog code below so that it matches the illustration, similar to the one on the previous page.

Complete the Verilog.

Use parameters for the bit widths wh and wa.

The registers inferred from the Verilog must match the diagram.

### module mac2

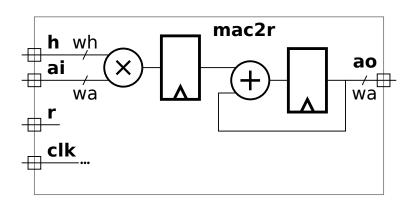

Problem 2: [20 pts] The mac (multiply-accumulate) modules compute a running sum of products. The alert student might have noticed that there is no way to reset the sum. In this problem a reset will be added.

The module below has an input r (for reset) which is to work as follows: When r=1 at a positive edge the product h\*ai should start a new running sum. That is, that particular h\*ai should be added to zero. When r=0 at a positive edge the product h\*ai should be added to the sum of the previous products. (If r=0 is always true then the hardware as illustrated works correctly.)

Add hardware to the diagram to implement the reset.  $\Box$  Complete the Verilog to implement the reset.

Use parameters for the bit widths wh and wa.

The registers inferred from the Verilog must match the diagram and  $\Box$  be sure that the reset is applied to the correct value.

module mac2r

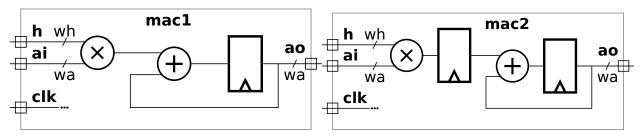

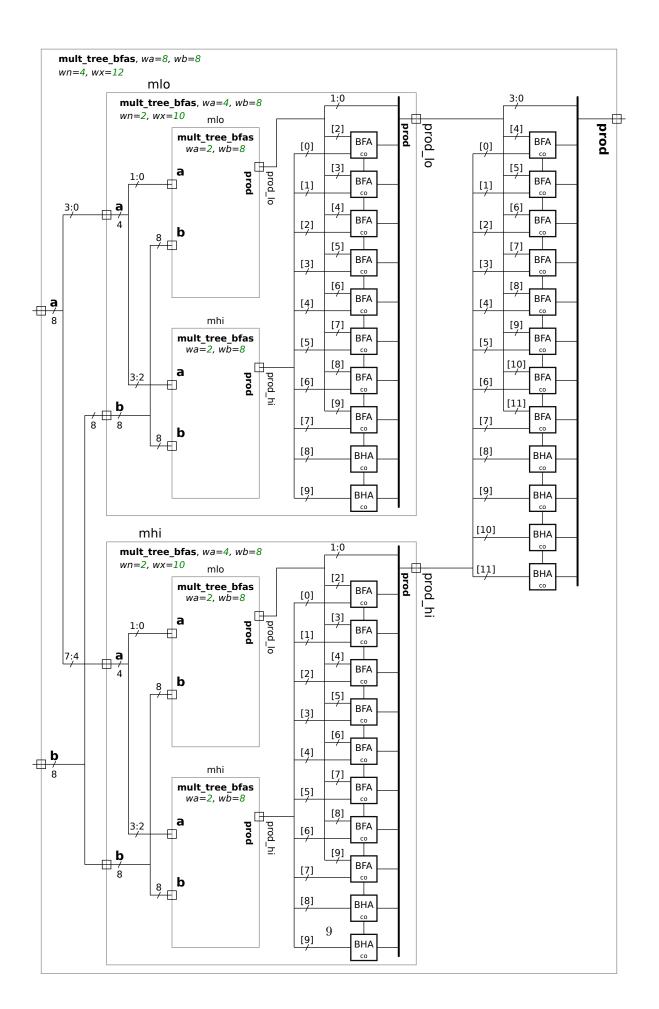

Problem 3: [20 pts] Appearing below are the modules from the previous problem. Suppose that in the multiplier below bit i of the product were computed in time  $[4i + 2] u_t$  and that a ripple adder were used for the sum. Let w denote the value of wh and wa (which means wh==wa).

(a) Find the minimum clock period for each using the simple model, and taking into account cascading. (The clock period is the length of the critical path, including the register delay.)

Find the clock period for mac1 with cascading.  $\Box$  Don't forget to include the delay of the register.

Find the clock period for mac2 with cascading.  $\Box$  Don't forget to include the delay of the registers.

(b) Find the minimum clock period for each using the simple model assuming that the multiplier output and adder input could not cascade.

Find the clock period for mac1 without cascading. 🗌 Don't forget to include the delay of the register.

Find the clock period for mac2 without cascading.  $\Box$  Don't forget to include the delay of the registers.

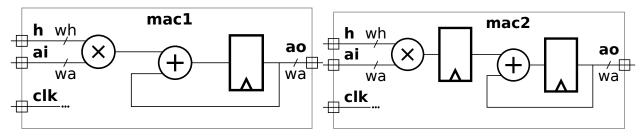

Problem 4: [20 pts] Appearing below is a recursively defined multiplier constructed using bfa (binary full adder) and bha (binary half adder) modules.

```

module mult tree bfas #( int wa = 16, int wb = wa, int wp = wa + wb )

( output uwire [wp-1:0] prod, input uwire [wa-1:0] a, input uwire [wb-1:0] b );

if (wa == 1) begin

assign prod = a ? b : 0;

end else begin

// Split a in half and recursively instantiate a module for each half.

localparam int wn = wa / 2;

localparam int wx = wb + wn;

uwire [wx-1:0] prod_lo, prod_hi;

mult_tree_bfas #(wn,wb) mlo( prod_lo, a[wn-1:0], b );

mult_tree_bfas #(wn,wb) mhi( prod_hi, a[wa-1:wn], b );

assign prod[wn-1:0] = prod_lo[wn-1:0];

uwire c[wp-1:wn-1];

assign c[wn-1] = 0;

for ( genvar i=wn; i<wx; i++ )</pre>

bfa b( c[i], prod[i], prod_lo[i],

prod_hi[i-wn], c[i-1] );

for ( genvar i=wx; i<wx+wn; i++ )</pre>

bha b( c[i], prod[i], prod_hi[i-wn],