## **LSU EE 4755**

**Problem 1:** The homework Verilog file, hw05.v, contains something similar to the streamlined multiplier presented in class, mult\_seq\_stream, and even more streamlined versions of the multiplier, mult\_seq\_stream\_2, and mult\_seq\_stream\_3. These modules are reproduced at the end of this assignment. For an HTML version visit

http://www.ece.lsu.edu/koppel/v/2015/hw05.v.html. See the 2014 midterm exam for similar problems.

(a) Show the hardware that will be synthesized for each module for the default parameters. Show the module after optimization.

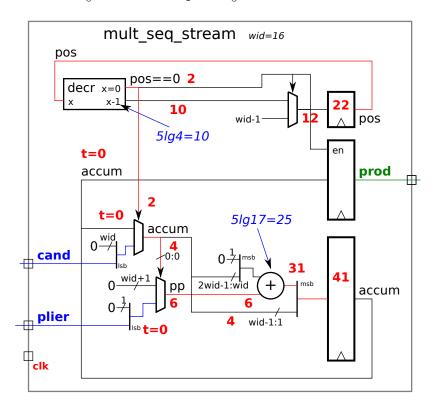

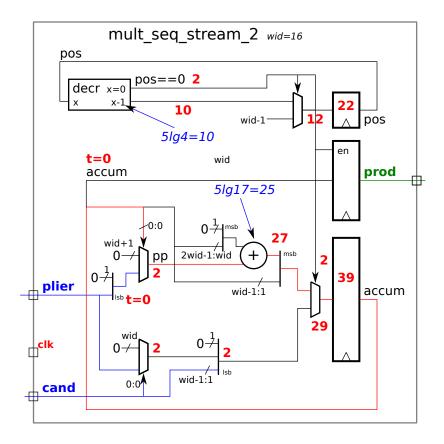

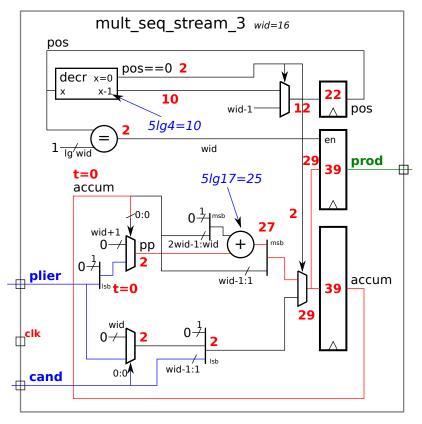

The synthesized hardware for each module appears below, and they also appear next to the respective Verilog descriptions at the end of this assignment. The red numbers show signal arrival times based on the assumptions given in the sub-problem below. The red wires show the critical path based on this analysis.

A decr unit has been used compute both pos-1 and pos==0, under the assumption that it might be possible to share some hardware. An enable signal is used on the prod register.

(b) Estimate the clock frequency of each module based on the following latencies:

Latch delay: 10 units. Multiplexor latency: 2 units. Latency of an *n*-bit adder:  $5\lceil \lg n \rceil$  units. Latency of an *n*-input gate:  $\lceil \lg n \rceil$  units. Let a unit be equal to 10 ps. Note: The duration of a unit was not given in the original assignment.

The timing analysis is shown in red on the three modules and the wires carrying the critical path are shown in red. This timing analysis strictly follows the guidelines above, using a  $5\lceil \lg 17 \rceil = 25$  unit delay for the big adder. Realistically, that would be a 16-bit adder with a carry out. Solutions that used 20 rather than 25 units for the adder are correct.

For mult\_seq\_stream the critical path ends at accum with a period of 41 units or 410 ps. That would give a clock frequency of  $\frac{1}{41}$  cycles per unit or 2.44 GHz.

For mult\_seq\_stream\_2 and mult\_seq\_stream\_3 the critical path is 2 units shorter, at 39 units. This is because the big adder uses the accum signal right out of the register outputs, in contrast to mult\_seq\_stream in which the particular accum to use must be routed through a mux based on a pos==0 select, adding delay. The clock frequency for these two modules would be 2.56 GHz.

(c) Why would module mult\_seq\_stream\_3 provide a result in less time than the other two, even assuming that the clock frequency for all the modules was the same?

The product is available one cycle earlier because it is written to **prod** from the output of the big adder rather than from **accum**.

```

mult_seq_stream wid=16

pos

pos = = 0 2

decr x=0

x-1

10

module mult_seq_stream

wid-1

pos

#( int wid = 16 )

5lg4=10

( output logic [2*wid-1:0] prod,

en

t=0

input logic [wid-1:0] plier,

accum

prod

曲

input logic [wid-1:0] cand,

2

input clk);

t=0

5lg17=25

accum

wid

localparam int wlog =

0-

4

-0:0

cand

$clog2(wid);

T.

31

41

wid+1

0

2wid-1:wid

+

pp

msb

accum

logic [wlog-1:0] pos;

6

Λ

plier

logic [2*wid-1:0] accum;

4

wid-1:1

t=0

ф<sub>сік</sub>

always @( posedge clk ) begin

logic [wid:0] pp;

if ( pos == 0 ) begin

prod = accum;

accum = cand;

pos = wid - 1;

end else begin

pos--;

end

// Note: the multiplicand is in the lower bits of the accumulator.

11

pp = accum[0] ? { 1'b0, plier } : 0;

// Add on the partial product and shift the accumulator.

11

accum = { { 1'b0, accum[2*wid-1:wid] } + pp, accum[wid-1:1] };

end

```

endmodule

```

mult_seq_stream_2 wid=16

pos

pos==0 2

decr x=0

x-1

10

wid-1

pos

5lg4=10

en

t=0

wid

accum

prod

ф

5lg17=25

module mult_seq_stream_2

0<sup>1</sup>/H<sup>msb</sup>

#( int wid = 16 )

-0:0

wid+1 🗴

( output logic [2*wid-1:0] prod,

2wid-1:wid

0 \rightarrow

рр

+

input logic [wid-1:0] plier,

39

0-

input logic [wid-1:0] cand,

plier

wid-1:1

accum

Isb t=0

input clk);

29

⊨<sup>clk</sup>

wid

localparam int wlog =

0≁

$clog2(wid);

logic [wlog-1:0] pos;

wid-1:1

____ cand

0:0^{\prime}

logic [2*wid-1:0] accum;

always @( posedge clk ) begin

if ( pos == 0 ) begin

prod = accum;

accum = { 1'b0, cand[0] ? plier : wid'(0), cand[wid-1:1] };

pos = wid - 1;

end else begin

logic [wid:0] pp;

// Note: the multiplicand is in the lower bits of the accumulator.

11

pp = accum[0] ? plier : 0;

// Add on the partial product and shift the accumulator.

11

accum = { { 1'b0, accum[2*wid-1:wid] } + pp, accum[wid-1:1] };

pos--;

end

end

```

endmodule

```

mult_seq_stream_3 wid=16

pos

pos = = 0 2

decr x=0

x-1

10

wid-1

pos

5lg4=10

en

1_{\text{Ig}'\text{wid}}

wid

module mult_seq_stream_3

prod

39

ф

t=0

#( int wid = 16 )

5lg17=25

accum

( output logic [2*wid-1:0] prod,

0<sup>1</sup>/H<sup>msb</sup>

input logic [wid-1:0] plier,

0:0

2

27

wid+1

input logic [wid-1:0] cand,

2wid-1:wid

0-

рр

+

input clk);

0

plier

accum

wid-1:1

Isb t=0

39

localparam int wlog =

$clog2(wid);

29

wid

⊨<sup>clk</sup>

0≁

logic [wlog-1:0] pos;

logic [2*wid-1:0] accum;

wid-1:1

____cand

0:0^{\prime}

always @( posedge clk ) begin

if ( pos == 0 ) begin

accum = { 1'b0, cand[0] ? plier : wid'(0), cand[wid-1:1] };

pos = wid - 1;

end else begin

logic [wid:0] pp;

// Note: the multiplicand is in the lower bits of the accumulator.

11

pp = accum[0] ? plier : 0;

// Add on the partial product and shift the accumulator.

11

accum = { { 1'b0, accum[2*wid-1:wid] } + pp, accum[wid-1:1] };

if ( pos == 1 ) prod = accum;

pos--;

end

end

```

endmodule