# A Performance Model and Efficiency-Based Assignment of Buffering Strategies for Automatic GPU Stencil Code Generation

Yue Hu<sup>1,2</sup>, David M. Koppelman<sup>1,2</sup>, and Steven R. Brandt<sup>1,3</sup>

<sup>1</sup>Center for Computation and Technology, Louisiana State University, Baton Rouge, LA, USA

<sup>2</sup>Division of Electrical & Computer Engineering, Louisiana State University, Baton Rouge, LA, USA

<sup>3</sup>Division of Computer Science, Louisiana State University, Baton Rouge, LA, USA

yhu14@lsu.edu, koppel@ece.lsu.edu, sbrandt@cct.lsu.edu

Abstract—Stencil computations form the basis for computer simulations across almost every field of science, such as computational fluid dynamics, data mining, and image processing. Their mostly regular data access patterns potentially enable them to take advantage of the high computation and data bandwidth of GPUs, but only if data buffering and other issues are handled properly.

Finding a good code generation presents a number of challenges, one of which is the best way to make use of memory. GPUs have three types of on-chip storage: registers, shared memory, and read-only cache. The choice of type of storage and how it's used, a buffering strategy, for each stencil array (grid function, (GF)) not only requires a good understanding of its stencil pattern, but also the efficiency of each type of storage for the GF, to avoid squandering storage that would be more beneficial to another GF. Our code-generation framework supports five buffering strategies. For a stencil computation with N GFs, the total number of possible assignments is  $5^N$ . Large, complex stencil kernels may consist of dozens of GFs, resulting in significant search overhead.

In this work, we present an analytic performance model for stencil computations on GPUs, and study the behavior of read-only cache and L2 cache. Next, we propose an efficiency-based assignment algorithm, which operates by scoring a change in buffering strategy for a GF using a combination of (a) the predicted execution time and (b) on-chip storage usage. By using this scoring an assignment for N GFs and b strategy types can be determined in (b-1)N(N+1)/2 steps. Results show that the performance model has good accuracy and that the assignment strategy is highly efficient.

# I. INTRODUCTION

Stencil computations' mostly regular data access patterns potentially enable them to take advantage of the high computation and data bandwidth of GPUs, but only if data buffering and other issues are handled properly. There have been a number of stencil frameworks [1], [2] designed to make it easier for programmers to write stencil codes and to generate good code, and in some cases that is done using auto-generation and autotuning of code. These frameworks evaluate proposed configurations using a performance model or a trial run. The latter method is time consuming, limiting configuration space exploration, especially when dynamic compilation is employed. But the configuration space that

must be searched for multi-level tuning can slow even model-driven autotuning techniques.

Assignment of a buffering strategy is challenging due to the multiple storage options available on some accelerators, and due to the fact that all must be used for bandwidth-limited code in order to realize the device's potential. With 5 possible strategies and 20 GFs, an exhaustive search would have to explore up to  $5^{20}\approx 9.54\times 10^{13}$  possibilities. The proposed efficiency-based assignment algorithm reduces this from  $b^N$  to (b-1)N(N+1)/2 evaluations, where N is the number of GFs and b is the number of buffering strategies.

To cull the search space, we need to understand the implications of buffering strategy choice on the efficiency of GPU execution. The use of registers and shared memory on the one hand, can reduce off-chip memory traffic while, on the other hand, may limit thread-level parallelism and that will result in poor latency hiding. Moreover, it is important to have an accurate prediction of the cache behavior. For example, is it wise to have more than one GF access the read-only cache? We are unable to give a good answer unless we can accurately predict the cache behavior, which is very challenging.

In this work, we firstly present an analytic performance model for stencil computations on GPUs. In addition, we design an efficiency-based assignment algorithm, in which an efficiency function is defined to select a proposal. A proposal is a change in buffering strategy of one GF. The efficiency function balances the performance improvement of the change with its resource consumption.

The main contributions of this work are:

- We present an accurate performance model which considers reduced data traffic at off-chip memory through buffering, as well as the side effect of low occupancy.

More importantly, the behavior of read-only cache and L2 cache is also studied.

- We design an efficiency-based assignment algorithm which can find suboptimal solution in  $O(N^2)$  time, instead of exponentially increasing design space with N, where N is the number of GFs in a kernel.

- The algorithm is evaluated using a micro-benchmark

and a number of real stencil applications.

The remainder of this paper is organized as follows. Related work, preliminaries, and background appear in Sec. II, III, and IV respectively. The performance model is presented in Sec. V, followed by the efficiency-based assignment in Sec. VI. Sec. VII and VIII discuss experimental methodology and results, and conclusions appear in Sec. IX.

#### II. RELATED WORK

# A. Performance Modeling

A reliable performance model is the foundation of model-driven autotuning technique. Hong et al. [3] propose an analytic GPU performance model, but their model is not suitable for autotuning stencil codes. Meng et al. [1] establish a performance model to autotune ghost zone for stencil computations on GPUs. However, since their main goal is the ghost zone study there are a number of important aspects are not considered. For example, their model only considers buffering with shared memory. Hu, et al. [4] present an analytic performance model for stencil computations on GPUs. Two buffering strategies: buffering with shared memory and buffering with shared memory and registers, are considered. Experiments show good prediction accuracy, but read-only cache strategy is not studied. Moreover, buffering strategies of all GFs in a kernel have to be identical.

#### B. Tradeoff of Buffering Strategies

Maruyama and Aoki [5] study a series of buffering methods for stencil computations, and they found shared memory and registers are very helpful, and read-only cache can noticeably increase performance as well. Yang et al. [6] found buffering too many GFs in shared memory would limit concurrency and degrade performance as well. Hayes and Zhang [7] observed that on-chip storage of GPUs should be utilized in a balance way. For example, it is necessary to offload the register pressure to shared memory when registers are the bottleneck for low concurrency. Gebhart et al. [8] proposed a reconfigurable on-chip storage design for GPUs. That is the relative size of registers, shared memory, and cache can be reconfigured based on fact that different codes favor different on-chip storage assignments.

#### III. PRELIMINARIES

The following is a brief description of the GPU used here, an NVIDIA Tesla K20xm. GPU execution starts with the *launch* of a *kernel* which executes as *g blocks* each consisting of *b* threads. Blocks are assigned to *SMs*, there are 14 in a K20xm. The block size, *b*, is limited by the resources available on an SM and the demands of the kernel. The resources include *shared* memory, 48 kiB, and *registers*,  $2^{16}$ . An SM also has a 48 kiB opt-in read-only (RO) cache. The small size and large latency of the L2 cache make it unsuitable for working set storage. (See Table IIIa for values of additional device parameters.) The maximum block size is

1024 threads. The latency of arithmetic instructions is high (by CPU standards), on the order of 11 cycles, and so a large number of threads is needed to hide this latency and so avoid underutilization. That's a concern for kernels with high per-thread shared memory or register demands, since they are limited to using fewer threads.

The issue rate varies by instruction, for double precision floating-point (FP) operations (including MADD operations) it is 64 instructions per cycle. At  $732\,\mathrm{MHz}$  that works out to  $1312\,\mathrm{GFLOPS}$  peak. Off-chip bandwidth is  $250\,\mathrm{GB/s}$ , which works out to computation to communication ratio of 42 (operations per element).

# IV. BACKGROUND

In preparation for *code generation* Chemora[9] generates *calculations* from a user-provided PDE system description. PDE  $\frac{dB}{dt} = \frac{\partial A}{\partial x^2}$  would be written as D\_t B = D\_xx A. A calculation is essentially the body of a loop nest iterating over a *grid space* of *grid points*. At run time the *Chemora code generator* generates a CUDA kernel from these calculations. The code generator decides how to assign grid points to threads and how best to handle data reuse. The above equation translates into something like the loop below:

for (i=imin to imax, j=jmin to jmax, k=kmin to kmax) RHS\_B[i,j,k]=(A[i,j-1,k]+2A[i,j,k]+A[i,j+1,k])/dxsq;

A and RHS\_B are 3D arrays called *grid functions* (GFs) and are indexed using loop indices and constant *offsets*. A *stencil* is the set of offsets for a particular GF. Reuse occurs in A due to the offsets, most elements being accessed three times. The example above consists of just a single GF write, but Chemora calculations can consist of any number of GF offset loads and stores and can use any number of intermediate variables and loop-invariant values.

The experienced reader may have recognized that for the loop above a good configuration might assign one block to each value of k, assign one thread in a block to each value of i (maximizing GPU memory request usage), and have threads iterate over j (so that values loaded in one iteration can be used in the next). The configuration might be modified if the loop over i is too short (multiple k's per block) or if it is too long (split i between blocks).

Chemora uses its performance model and efficiency-based algorithm to make such decisions. The goal is to choose a block configuration for the kernel and to choose a buffering strategy for each GF making use of any combination of available storage. A block configuration, denoted  $C_{\mathrm{Block}}$ , is specified by four values: an iteration direction  $e \in \{y, z\}$ , the dimensions of the grid space plane covered by the block's threads,  $t_x$  and  $t_f$ , and the number of grid points processed per thread along the e-axis,  $t_{\mathrm{ee}}$ , where f denotes the axis orthogonal to x-axis and e-axis.

An assignment,  $C_{\text{Assignment}} = (\mathbf{u}, \mathbf{r}, \mathbf{b}, \mathbf{p}, \mathbf{c})$ , is a mapping of GFs to strategies. Each set  $\mathbf{u}, \mathbf{r}, \mathbf{b}, \mathbf{p}$ , and  $\mathbf{c}$ , represents a different strategy. The grid functions are partitioned

| Parameter               | Description                                                                                    |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------|--|--|--|

| $C_{\mathrm{Block}}$    | Block configuration, $(e, t_x, t_f, t_{ee})$ .                                                 |  |  |  |

| e                       | Iteration axis, $e \in \{y, z\}$ . Also, $f \equiv \{y, z\} - \{e\}$ .                         |  |  |  |

| $t_{ m x}$              | Num. of threads per block along $x$ axis.                                                      |  |  |  |

| $t_{ m f}$              | Num. of threads per block along $f$ axis.                                                      |  |  |  |

| $t_{ m ee}$             | Number of iterations.                                                                          |  |  |  |

| $C_{\text{Assignment}}$ | Buffering strategy assignments, $(\mathbf{u}, \mathbf{r}, \mathbf{b}, \mathbf{p}, \mathbf{c})$ |  |  |  |

| u                       | Set of un-buffered GFs.                                                                        |  |  |  |

| r                       | Set of GFs buffered only with registers.                                                       |  |  |  |

| b                       | Set of GFs buffered only with shared memory.                                                   |  |  |  |

| р                       | Set of GFs buffered with registers and shared memory.                                          |  |  |  |

| С                       | Set of GFs buffered in read-only cache.                                                        |  |  |  |

Table I: Parameters for code generation and run.

among them. Table I lists the block configuration parameters and buffering strategies.

# A. Strategy u: Unbuffered

In the *unbuffered* strategy each offset load is realized by a global load instruction. Latency will be on the order of 189 cycles (L2 hit) to 300 cycles (L2 miss) and L2 misses consume off-chip bandwidth. Although the performance of the un-buffered strategy is relatively low, it uses no shared memory and the fewest registers, saving these resources for more performance-sensitive GFs.

#### B. Strategy r: Register

In the register strategy registers carry loaded values from one iteration to the next. It is applicable when the offset axis matches the iteration axis. This is the case in the example above if threads iterate in the i direction. Since there is less than one instruction per offset load, the strategy uses the least instruction bandwidth but consumes the most registers. For example, consider references to a GF at offsets A[0,1,0] and A[0,0,0] when iterating in the +j direction. A load would be generated for reference A[0,1,0] in one iteration and the loaded value would also be used for A[0,0,0] in the next iteration, eliminating the need for any instruction to load the value for the second reference (in all but the first iteration). However the register holding the value cannot be used for other purposes. Overuse of registers lowers occupancy and even result in register spills, causing significant performance degradation.

# C. Strategy b: Shared Only

In the *shared only* strategy, shared memory is used to hold GF elements. The amount of shared memory per GF is based on the volume of the grid points assigned to threads extended by the stencil offsets. The strategy also requires instructions to load shared memory and barriers to isolate shared memory updates. Because data buffered in shared memory can be accessed by all threads of a block, this buffering strategy can be applied to GFs with all types of stencil patterns. However, this strategy may require a large amount of shared memory, and so may result in a great drop in occupancy when it is applied.

# D. Strategy p: Plus

The plus strategy, referred to elsewhere as 2.5D tiling, is a hybrid of the shared-only and register strategies. Like the register strategy, a global load is performed for the GF access having offset  $(0, o_e, 0) \in \mathcal{S}$  with the largest  $o_e$ , and the value is kept in a register for use by offsets  $(0, d, 0) \in \mathcal{S} : d < o_e$ , where S is the stencil for the GF. The value is copied to shared memory for use by offsets  $(o_x, 0, o_f) \in \mathcal{S}$ . Global loads are used for all other offsets, such as (1, 1, 1). For example, suppose that iteration is along the y axis and the stencil for GF A is A[0,1,0], A[0,0,0], A[0,-1,0], A[1,1,0], A[1,0,1]. A global load will be used for A[0,1,0] and the loaded value will be used for A[0,0,0] and A[0,-1,0], shared memory will be used for A[1,0,1] and a global load for A[1,1,0]. The amount of shared memory is the grid space occupied by the threads extended by the stencil only in the axis normal to iteration, a significant savings.

# E. Strategy c: ROC (Read-Only Cache)

The *ROC* strategy uses read-only cache instructions for offset loads. This strategy consumes ROC space, but due to peculiarities of the NVIDIA Kepler instruction set (lack of immediate offsets), additional registers and arithmetic instructions are also used. As with any cache, performance depends upon several uncontrollable factors such as compiler instruction scheduling by the PTX compiler, warp execution ordering, and cache replacement.

### V. PERFORMANCE MODEL

The efficiency-based assignment algorithm relies upon a performance model that estimates the execution time of a calculation for some block configuration and assignment running on some GPU. This model accounts not just for the data volume differences between the different buffering strategies, but also for any exposed latencies in the instructions needed to implement them.

# A. Calculation Characterization

A calculation is characterized by a stencil for each input grid function, and three additional parameters: the number of FP operations, the number of GF stores, and the number of intermediate registers used. See Table IIa.

The stencil (not shown) for a GF is used to compute components of its stencil bounding box, see the top half of Table IIb. These are mainly used to calculate on-chip memory usage. For example,  $(t_x + s_x)(t_e + s_e)(t_f + s_f)$  elements of storage would be used for a GF under the buffered only with shared memory strategy.

Reuse factors, shown in the lower-half of the table, are computed from a GF's stencil once a block configuration and an assignment are chosen. These indicate the number of memory accesses performed per grid point for different axis alignments. For example,  $r_e$  is the number of accesses

| Parameter                           | Description                                                |  |  |

|-------------------------------------|------------------------------------------------------------|--|--|

| $n_{\mathrm{reg}}^{\mathrm{inter}}$ | Number of registers used to store intermediate values      |  |  |

| $n_{ m gf}^{ m st}$                 | Number of GF stores                                        |  |  |

| $n_{\mathrm{fp}}$                   | Number of FP operations it takes to calculate a grid point |  |  |

#### (a) Calculation parameters (except GF loads).

| Parameter         | Description                                                                        |  |  |  |

|-------------------|------------------------------------------------------------------------------------|--|--|--|

| $s_{\mathrm{x}}$  | $s_{\rm x} = s_{\rm xn} + s_{\rm xp}$                                              |  |  |  |

| $s_{ m xn}$       | Magnitude of minimum $x$ offset.                                                   |  |  |  |

| $s_{\mathrm{xp}}$ | Magnitude of maximum $x$ offset.                                                   |  |  |  |

| $s_{ m f}$        | Difference between maximum and minimum $f$ offset.                                 |  |  |  |

| $s_{ m e}$        | Difference between maximum and minimum $e$ offset.                                 |  |  |  |

| r                 | Re-use factor for all offsets. $r = r_{\rm x} + r_{\rm f} + r_{\rm e} + r_{\rm o}$ |  |  |  |

| $r_{\mathrm{x}}$  | Number of offsets $(o_x, o_e, o_f)$ : $o_x \neq 0$ , $o_e = o_f = 0$ .             |  |  |  |

| $r_{ m f}$        | Number of offsets $(o_x, o_e, o_f)$ : $o_e = 0, o_f \neq 0$ .                      |  |  |  |

| $r_{ m e}$        | Number of offsets $(o_x, o_e, o_f)$ : $o_e \neq 0$ , $o_x = o_f = 0$ .             |  |  |  |

| $r_{ m o}$        | Number of offsets $(o_x, o_e, o_f)$ : $o_e \neq 0$ , $ o_x  +  o_f  \neq 0$ .      |  |  |  |

(b) GF load parameters derived from its offsets.

Table II: Model input.

with offsets along the e-axis. These are used to estimate hit ratios in the read-only and L2 caches.

## B. GPU Characterization

Table IIIa shows hardware-related parameters and their values for NVIDIA GPU K20xm. Parameters  $K_{\rm reg}$ ,  $K_{\rm smem}$ , and  $K_{\rm roc}$  are obtained from the product literature [10]. The other parameters are measured using micro-benchmarks. Details on micro-benchmarks will not be discussed in this paper due to limited space. Table IIIb lists parameters that are hard to obtain but important to performance modeling. These parameters are determined by hardware device, compiler, and stencil applications. For example,  $\lambda_{\rm g}$  is proportional to the number of registers allocated for data loaded from global memory. It could be as small as one when only one register is allocated. Therefore, for these parameters we estimate their values to the best of our knowledge.

| $\mathcal{E}$       |                                              |                   |  |  |

|---------------------|----------------------------------------------|-------------------|--|--|

| Parameter           | Parameter Description                        |                   |  |  |

| $W_{L2}$            | W <sub>L2</sub> Measured L2 cache bandwidth* |                   |  |  |

| $W_{GM}$            | Measured global memory bandwidth*            | 1.92 (157.5 GB/s) |  |  |

| $L_{\rm g}$         | Global memory latency (cycles)               | 305               |  |  |

| $L_{L2}$            |                                              |                   |  |  |

| $L_{\rm s}$         | $L_{\rm s}$ Shared memory latency (cycles)   |                   |  |  |

| $L_{ m b}$          | L <sub>b</sub> Barrier latency (cycles)      |                   |  |  |

| $L_{\rm c}$         | Read-only cache latency (cycles)             | 108               |  |  |

| $L_{\mathrm{f}}$    | FP operation latency (cycles)                | 10                |  |  |

| $LS_c$              | Line size of read-only cache (elts)          | 16                |  |  |

| $LS_{L2}$           | Line size of L2 cache (elts)                 | 4                 |  |  |

| $K_{\text{reg}}$    | Register file capacity (elts/SM)             | 32768             |  |  |

| $K_{\mathrm{smem}}$ | Shared memory capacity (elts/SM)             | 6144 (48 kiB)     |  |  |

| $K_{\rm roc}$       | Read-only cache capacity (elts/SM)           | 6144 (48 kiB)     |  |  |

#### (a) Hardware parameters. \*unit: elements (elts) / cycle / SM.

| Parameter   | Description                                          |     |  |

|-------------|------------------------------------------------------|-----|--|

| $\lambda_g$ | Parallel factor for global memory access             |     |  |

| $\lambda_s$ | Parallel factor for shared memory access             |     |  |

| $\lambda_b$ | Parallel factor for barrier synchronization overhead |     |  |

| $\lambda_c$ | Parallel factor for read-only cache access           | 3   |  |

| $\lambda_f$ | Parallel factor for FP operation                     |     |  |

| $L_{\rm o}$ | Overhead in cycle per iteration per thread block     | 100 |  |

(b) Software parameters.

Table III: Parameters used for modeling on GPU K20xm

#### C. Execution Time Prediction

| $D_{ m total}^{ m L2}$         | $D_{\rm u}^{\rm L2} + D_{\rm r}^{\rm L2} + D_{\rm b}^{\rm L2} + D_{\rm p}^{\rm L2} + D_{\rm c}^{\rm L2} + \alpha n_{\rm gf}^{\rm st}$                                                                                                                                                            |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\alpha$                       | $\lceil t_{ m x}  ceil^{\langle + { m L2}  angle} / t_{ m x}$                                                                                                                                                                                                                                    |

| $D_{\mathrm{u}}^{\mathrm{L2}}$ | $\sum_{i \in \mathbf{u}} (1 + r_i) \alpha$                                                                                                                                                                                                                                                       |

| $D_{\mathrm{r}}^{\mathrm{L2}}$ | $\sum_{i \in \mathbf{r}} (1 + \frac{s_{e_i}}{t_{ee}}) \alpha$                                                                                                                                                                                                                                    |

| $D_{ m b}^{ m L2}$             | $\sum_{i \in \mathbf{b}} \lceil s_{\mathbf{x}_i} + t_{\mathbf{x}} \rceil^{\langle +\text{L2} \rangle} (s_{\mathbf{f}_i} + t_{\mathbf{f}}) (s_{\mathbf{e}_i} + t_{\mathbf{ee}}) / t_{\mathbf{x}} t_{\mathbf{f}} t_{\mathbf{ee}}$                                                                  |

| $D_{\mathrm{p}}^{\mathrm{L2}}$ | $\sum_{i \in \mathbf{p}} \alpha \left( r_{o_i} + 1 + \frac{s_{e_i}}{t_{ee}} + \frac{s_{f_i}}{t_f} \right) + \left( \left\lceil s_{\mathbf{xn}_i} \right\rceil^{\langle \mathbf{L2} \rangle} + \left\lceil s_{\mathbf{xp}_i} \right\rceil^{\langle \mathbf{L2} \rangle} \right) / t_{\mathbf{x}}$ |

| $D_{\mathrm{c}}^{\mathrm{L2}}$ | $\left(M_{\text{roc}} + \sum_{i \in \mathbf{c}} (r_{e_i} + r_{o_i})(1 - \sqrt{R_{\text{SND}}^{\text{RO}}}) t_{\mathbf{x}} t_{\mathbf{f}}\right) / t_{\mathbf{x}} t_{\mathbf{f}}$                                                                                                                 |

| $M_{\rm roc}$                  | $\sum_{i \in \mathbf{c}} \lceil s_{\mathbf{x}_i} + t_{\mathbf{x}} \rceil^{\langle +c \rangle} (1 + s_{\mathbf{f}_i}) t_{\mathbf{f}}$                                                                                                                                                             |

| $R_{ m SND}^{ m RO}$           | $K_{ m RO}/M_{ m roc}$                                                                                                                                                                                                                                                                           |

#### (a) Volume of data traffic at the L2 cache

| $D_{ m total}^{ m GM}$         | $D_{\rm u}^{\rm GM} + D_{\rm r}^{\rm GM} + D_{\rm b}^{\rm GM} + D_{\rm p}^{\rm GM} + D_{\rm c}^{\rm GM} + \alpha n_{\rm gf}^{\rm st}$                                                                                 |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $D_{\mathrm{r}}^{\mathrm{GM}}$ | $D_{ m r}^{ m L2}$                                                                                                                                                                                                    |

| $D_{ m b}^{ m GM}$             | $D_{ m b}^{ m L2}$                                                                                                                                                                                                    |

| $D_{\mathrm{p}}^{\mathrm{GM}}$ | $D_{ m p}^{ m L2}$                                                                                                                                                                                                    |

| $D_{\mathrm{u}}^{\mathrm{GM}}$ | $\left(M_{\mathrm{u}}^{\mathrm{L2}} + \sum_{i \in \mathbf{u}} (r_{\mathrm{e}_i} + r_{\mathrm{o}_i}) (1 - \sqrt{R_{\mathrm{SND}}^{\mathrm{L2}}}) t_{\mathrm{x}} t_{\mathrm{f}}\right) / t_{\mathrm{x}} t_{\mathrm{f}}$ |

| $D_{\rm c}^{ m GM}$            | $\left(M_{\rm c}^{\rm L2} + \sum_{i \in \mathbf{c}} (r_{\rm e_i} + r_{\rm o_i}) (1 - \sqrt{R_{\rm SND}^{\rm L2}}) t_{\rm x} t_{\rm f}\right) / t_{\rm x} t_{\rm f}$                                                   |

| $R_{ m SND}^{ m L2}$           | $M_{\mathrm{u}}^{\mathrm{L2}} = \sum_{i \in \mathbf{u}} \lceil s_{\mathrm{x}_i} + t_{\mathrm{x}} \rceil^{\langle +\mathrm{L2} \rangle} (1 + s_{\mathrm{f}_i}) t_{\mathrm{f}}$                                         |

|                                | $M_{ m r}^{ m L2} = \sum_{i \in {f r}} \lceil t_{ m x}  ceil^{\langle + { m L2}  angle} t_{ m f}$                                                                                                                     |

|                                | $M_{\mathrm{b\&p}}^{\mathrm{L2}} = \sum_{i \in \mathbf{b} \cup \mathbf{p}} \lceil s_{\mathrm{x}_i} + t_{\mathrm{x}} \rceil^{\langle +\mathrm{L2} \rangle} (t_{\mathrm{f}} + s_{\mathrm{f}_i})$                        |

|                                | $M_{\mathrm{c}}^{\mathrm{L2}} = \sum_{i \in \mathbf{c}} \lceil s_{\mathrm{x}_i} + t_{\mathrm{x}} \rceil^{\langle + \mathrm{c} \rangle}$                                                                               |

|                                | $\times \left(R_{ m SND}^{ m RO} > 1?(t_{ m f} + s_{ m f_i}) : (1 + s_{ m f_i})t_{ m f}(1 - \sqrt{R_{ m SND}^{ m RO}})\right)$                                                                                        |

|                                | $R_{\text{SND}}^{\text{L2}} = K_{\text{L2}} / \left[ N_{\text{SM}} \left( M_{\text{u}}^{\text{L2}} + M_{\text{r}}^{\text{L2}} + M_{\text{b\&p}}^{\text{L2}} + M_{\text{c}}^{\text{L2}} \right) \right]$               |

# (b) Volume of data traffic at global memory

| $T_{ m lat}$     | $(N_{\rm g}L_{\rm g} + N_{\rm L2}L_{\rm L2} + N_{\rm s}L_{\rm s} + N_{\rm b}L_{\rm b} + N_{\rm c}L_{\rm c} + n_{\rm fp}L_{\rm f} + L_{\rm m})/t_{\rm x}t_{\rm f}$ |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $N_{\mathrm{g}}$ | $\left\lceil D_{	ext{total}}^{	ext{GM}}/\lambda_{	ext{g}} ight ceil$                                                                                              |

| $N_{\rm L2}$     | $\left\lceil D_{ m total}^{ m L2}/\lambda_{ m L2} ight ceil$                                                                                                      |

| $N_{ m s}$       | $\left[\left(\sum_{i\in\mathbf{b}}r_{i}+\sum_{i\in\mathbf{p}}\left(r_{\mathbf{x}_{i}}+r_{\mathbf{f}_{i}}\right)\right)/\lambda_{\mathbf{s}}\right]$               |

| $N_{ m b}$       | $\lceil \left(  \mathbf{b}  +  \mathbf{p}  \right) / \lambda_{\mathrm{b}} \rceil$                                                                                 |

| $N_{\rm c}$      | $\left[D_{ m c}^{ m L2}/\lambda_{ m c} ight]$                                                                                                                     |

## (c) Operation latency

| $M_{\text{reg}}$ | $t_{\mathbf{x}}t_{\mathbf{f}}(n_{\text{reg}}^{\text{inter}} +  \mathbf{u}  +  \mathbf{b}  +  \mathbf{c}  + \sum_{i \in \mathbf{r} \cup \mathbf{p}} (1 + s_{e_i})) \le K_{\text{reg}}$ |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $M_{ m smem}$    | $\sum_{i \in \mathbf{b}} (s_{x_i} + t_x)(s_{f_i} + t_f)(s_{e_i} + 1) + \sum_{i \in \mathbf{p}} (s_{x_i} + t_x)(s_{f_i} + t_f)$                                                        |

|                  | $\leq K_{\mathrm{smem}}$                                                                                                                                                              |

# (d) Resource Usage and Constraints

Table IV: Equations used for performance modeling

The execution time model considers three factors, kernel launch overhead,  $T_{\rm launch}$ , data traffic,  $T_{\rm data}$ , and exposed latency,  $T_{\rm lat}$ . Exposed latency is the execution time when accounting for operation latency (including arithmetic and memory accesses) but ignoring memory congestion and issue bandwidth. It is possible in some situations to schedule instructions such that execution time is determined only by the larger of the two latter factors:  $T_{\rm tot} = T_{\rm launch} + \max\{T_{\rm data}, T_{\rm lat}\}$ .

When loads are bunched together and near consuming instructions data bandwidth time cannot be hidden, in the worst case  $T_{\rm tot} = T_{\rm launch} + T_{\rm data} + T_{\rm lat}$ . The more common

intermediate cases are modeled with:

$$T_{\text{tot}} = T_{\text{launch}} + \beta \max (T_{\text{data}}, T_{\text{lat}}) + (1 - \beta) (T_{\text{data}} + T_{\text{lat}}) / 2,$$

(1)

where  $\beta \in [0,1]$  is the degree of non-interference of the two factors. An empirically determined value of .8 works well for the codes studied. Assuming the bottleneck of data traffic is either L2 cache or global memory, we have:

$$T_{\text{data}} = \max \left( D_{\text{total}}^{\text{L2}} / W_{\text{L2}}, D_{\text{total}}^{\text{GM}} / W_{\text{GM}} \right)$$

(2)

where  $D_{\rm total}^{\rm L2}$  denotes the total volume data loaded from and stored to the L2 cache, while  $W_{\rm L2}$  denotes the realistically achievable bandwidth. The definitions of  $D_{\rm total}^{\rm GM}$  and  $W_{\rm GM}$  are similar. Note the unit of data volume is the number of data elements it takes to compute a grid point.

1) Traffic between the L2 Cache and SM: The total volume of data traffic between the L2 and SM cache consists of six parts as shown in Table IVa. These are shown using round-to-line operators  $\lceil a \rceil^{\langle C \rangle} \equiv \lceil a/LS_C \rceil LS_C$  and  $\lceil a \rceil^{\langle +C \rangle} \equiv \lceil a/LS_C + \frac{1}{2} \rceil LS_C$ . The first five parts:  $D_{\rm u}^{\rm L2}$ ,  $D_{\rm r}^{\rm L2}$ ,  $D_{\rm b}^{\rm L2}$ ,  $D_{\rm p}^{\rm L2}$ , and  $D_{\rm c}^{\rm L2}$  are for L2 cache reads from GFs with different buffering strategies. The last part  $\alpha n_{\rm gf}^{\rm st}$  is for L2 cache writes, where  $\alpha$  is defined for the overhead of possible unaligned accesses.

For the unbuffered case  $D_{\rm u}^{\rm L2}$ , all reads are directed to the L2 cache, while the buffered cases have fewer reads. Take  $D_{\rm r}^{\rm L2}$ ,  $D_{\rm b}^{\rm L2}$ , and  $D_{\rm p}^{\rm L2}$  for example. The reads are for loading data to on-chip memory in an iteration are independent of a GF's data reuse  $r_{\rm i}$ . Note for  $D_{\rm p}^{\rm L2}$ , only data along iteration direction E, and the one on XF plane that is orthogonal to E can be buffered as discussed in Section IV-D. Therefore irregular points (i.e.  $r_o$ ), if they exist, are left unbuffered.

Equation  $D_{\rm c}^{\rm L2}$  needs care as it depends on the read-only cache's behavior. It consists of two parts:  $M_{\rm roc}$  for cold misses and the others for capacity misses.  $M_{\rm roc}$  is equal to both the volume of data brought to the cache for the first time, and the minimum cache size to eliminate capacity misses in the equation for  $R_{\rm SND}^{\rm RO}$  in Table IVa. Note here we assume data reuse on the read-only cache exists only along the X direction. The Supply and Demand Ratio of the read-only cache,  $R_{\rm SND}^{\rm RO}$ , is used to model the impact of capacity misses which exist when  $R_{\rm SND}^{\rm RO}$  is smaller than one.

2) Volume of traffic at global memory: Similarly, Table IVb lists the equations for computing the total volume of data traffic at global memory. For  $D_{\rm r}^{\rm GM}$ ,  $D_{\rm b}^{\rm GM}$ , and  $D_{\rm p}^{\rm GM}$ , the data has no reuse so the volume of global memory is equal to the volume of L2 cache.

Equation  $D_{\rm u}^{\rm GM}$  and  $D_{\rm c}^{\rm GM}$  needs care as the L2 cache is shown to be helpful in reducing traffic to global memory for data with reuse. Similarly  $R_{\rm SND}^{\rm L2}$ , the Supply and Demand Ratio of the L2 cache, is used to model the impact of capacity misses.  $M_{\rm u}^{\rm L2}$ ,  $M_{\rm r}^{\rm L2}$ ,  $M_{\rm b}^{\rm L2}$ , and  $M_{\rm c}^{\rm L2}$  denote the minimum L2 cache size that is required to avoid capacity misses by GFs buffered in different strategies.  $N_{\rm SM}$  denotes threads running on all SMs are sharing the same L2 cache.

3) Analysis of exposed latency: To quantify the impact of thread-level parallelism on execution time, we propose a model in Table IVc where exposed latency is high when thread-level parallelism (i.e. smaller  $t_x t_f$ ) is low.

In addition to parallelism, various operation latencies have impact on  $T_{\rm lat}$ . The latencies we modeled include global memory accesses, L2 cache accesses, shared memory accesses, barrier operations, read-only cache accesses, floating point operations, and a thread block's time overhead  $L_{\rm m}$  per iteration. The parameter  $\lambda_{\rm g}$  represents the number of global memory load and store instructions that can be issued in parallel. Correspondingly,  $N_{\rm g}L_{\rm g}$  denotes the exposed latency from global memory accesses. The definitions for the other N's, L's, and  $\lambda$ 's are similar.

# D. On-Chip Memory Usage Affects Parallelism

Table IVd shows how usage of registers and shared memory affects parallelism. We can use the two inequalities in Table IVd to solve for the variables  $t_{\rm f}$ , given a value for  $t_{\rm x}$ . This gives us the block configuration  $C_{\rm Block}$ .

# VI. EFFICIENCY-BASED ASSIGNMENT

# Algorithm 1 Efficiency-based on-chip memory allocation

```

1: Gather metadata of n GFs

2: Initialize C_{\text{Assignment}}: \mathbf{u} = \{1, 2, ..., n\} and \mathbf{r} = \mathbf{b} =

\mathbf{p} = \mathbf{c} = \{\}

3: next = true

while next do

m_{\rm rbp} = m_{\rm c} = NULL

5:

for (i \in \mathbf{u}) \& (r_i > 0) do

6:

for every \{r, b, p, c\} as target set t do

7:

//Propose a move m: move i from \mathbf{u} to \mathbf{t}

8:

if m is invalid then

9:

continue

10:

end if

11:

if t is not c then

12:

13:

m_{\mathrm{rbp}} = m \text{ if } \mathcal{E}(m) > \mathcal{E}(m_{\mathrm{rbp}})

14:

m_{\rm c} = m \text{ if } \mathcal{E}(m) > \mathcal{E}(m_{\rm c})

15:

16:

17:

end for

18:

end for

if \min(\triangle T(\mathfrak{m}_{\rm rbp}), \triangle T(\mathfrak{m}_{\rm c})) > 0 then

19:

next = false

20:

21:

else

if \triangle T(\mathsf{M}_{\mathsf{rbp}}) < \triangle T(\mathsf{M}_{\mathsf{c}}) then

22:

23:

Accept Mrbp

else

24:

25:

Accept Mc

end if

26:

end if

28: end while

```

Let  $C = \{\mathbf{u}, \mathbf{r}, \mathbf{b}, \mathbf{p}, \mathbf{c}\}$  be some incomplete assignment and let m denote a proposed reassignment of some  $gf \in \mathbf{u}$ .

At the heart of the efficiency-based assignment algorithm is an efficiency function,  $\mathcal{E}(C,\mathfrak{m})\in R$ , which gives the efficiency (desirability) of assignment  $\mathfrak{m}$  given an incomplete assignment C. The efficiency function is evaluated for all moves from an incomplete assignment, the best of which is used to generate a new (possibly) incomplete assignment. The efficiency function has been designed to avoid backtracking, so that an entire assignment can be computed in (b-1)N(N+1)/2 steps where b and N denote the number of buffering strategies and GFs separately, as compared to  $b^N$  steps for an exhaustive search.

Algorithm 1 shows how on-chip memory is allocated to improve performance step-by-step in a memory-efficient way. At the beginning, all GFs are un-buffered. Line6-7: shows all possible moves  $\mathbb M$  to buffer an un-buffered GF in one of four different ways. Note that GFs must have data reuse (i.e.  $r_{\rm i}>0$ ) to be buffered. Line9-11: a proposed move  $\mathbb M$  could be invalid when a buffering strategy does not apply to a GF due to its stencil pattern.

The performance improvement of a move  ${\tt m}$  is defined by  $\triangle T$ , which denotes the change in execution time. We define the efficiency function  $\mathcal{E}({\tt m})$ , Eq 3, to identify steps that reduce the execution time, but at the same time to penalize changes that take too much memory and reward changes that reduce memory. Buffering a GF may reduce memory since it may reduce the number of threads while, for example, the number of used registers per thread is kept constant. The variables  $is_{\text{reg\_limited}}$ ,  $is_{\text{smem\_limited}}$ , and  $is_{\text{roc\_limited}}$  are either 1 or 0 and denote whether on-chip memory (in the form of registers, shared memory, or read-only cache) is limited or not. For example,  $is_{\text{reg\_limited}}$  is 0 if the number of registers is large enough to buffer all unbuffered GFs at the same occupancy.

$$\begin{split} \mathcal{E}(\mathbf{m}) = & - \Delta T(\mathbf{m}) \left( \exp\left(-is_{\text{reg\_limited}} \triangle M_{\text{reg}}/K_{\text{reg}}\right) \right. \\ & + \left. \exp\left(-is_{\text{smem\_limited}} \triangle M_{\text{smem}}/K_{\text{smem}}\right) \right. \\ & + \left. \exp\left(-is_{\text{roc\_limited}} \triangle M_{\text{roc}}/K_{\text{roc}}\right)\right) \end{split}$$

L12-16:  $m_{\rm rbp}$  is the most efficient move for strategies that buffer in registers, shared memory, and shared memory and registers, while  $m_{\rm c}$  is the most efficient strategy for buffering in read-only cache. The reason we have two types of most efficient move is  $M_{\rm roc}$  denotes the minimum cache size to avoid a capacity miss. Unlike  $M_{\rm reg} \leq K_{\rm reg}$  and  $M_{\rm smem} \leq K_{\rm smem}$ ,  $M_{\rm roc}$  could be greater than  $K_{\rm roc}$ .

L19-21: the algorithm terminates when the execution time cannot be reduced. L22-26: accept  $m_{\rm rbp}$  or  $m_{\rm c}$  depending on which one results in greater execution time drop.

# VII. EXPERIMENTAL METHODOLOGY

The efficiency-based assignment algorithm was evaluated in a set of runs on a system consisting of an Intel Xeon E5-2670 CPU and an NVIDIA Tesla K20xm GPU. The GPU

| Kernel name   | Input GFs | $n_{\mathrm{gf}}^{st}$ | $n_{ m fp}$ | Problem Size |

|---------------|-----------|------------------------|-------------|--------------|

| Micro-bench   | 10 [10]   | 1                      | 180         | 256×256×256  |

| Fluam_RK3_1   | 5 [5]     | 4                      | 395         | 256×256×256  |

| Fluam_RK3_2   | 4 [1]     | 4                      | 33          | 256×256×256  |

| Scale_1       | 5 [2]     | 3                      | 0           | 32×32×1280   |

| Scale_2       | 9 [1]     | 8                      | 55          | 32×32×1280   |

| BSSN_Advect   | 24 [24]   | 25                     | 3160        | 100×100×100  |

| BSSN_Dalpha_1 | 15 [15]   | 26                     | 401         | 100×100×100  |

Table V: Stencil Application Characteristics. Number of GF with reuse shown in brackets. See Table IIa for definition of  $n_{\rm ef}^{\rm st}$  and  $n_{\rm fp}$ . Problem size excludes boundary.

code was prepared with CUDA version 6.0.1. In addition, a micro-benchmark and a number of real-world applications are used for evaluation. Table V lists their characteristics.

The micro-benchmark we designed is a 3D stencil computation with one output GF B and ten input GFs  $A_n$ ,  $n \in \{0,1,\ldots,9\}$ , as shown in Eq 4.  $c_n[m]$  with  $m \in \{0,1,\ldots,8\}$  are constants with different values. The stencil pattern of GF  $A_n$  is the same as that of a GF in a real-world application *Fluam*. We designed such micro-benchmark for three reasons. First, we expect it to be representative of a class of real applications. Second, all input GFs have the same stencil pattern making it easy to demonstrate the performance model. Third, the benchmark has enough GFs so that an efficiency-based assignment algorithm is needed to search the design space.

$$B[i,j,k] + \sum_{n=0}^{9} (c_n[0] \times A_n[n,i,j,k]$$

$$+ c_n[1] \times A_n[i-1,j,k] + c_n[2] \times A_n[i+1,j,k]$$

$$+ c_n[3] \times A_n[i,j-1,k] + c_n[4] \times A_n[i,j+1,k]$$

$$+ c_n[5] \times A_n[i,j,k-1] + c_n[6] \times A_n[i,j,k+1]$$

$$+ c_n[7] \times A_n[i-1,j+1,k] + c_n[8] \times A_n[i-1,j,k+1] )$$

(4)

Fluam [11] is a GPU application (in CUDA C) developed for fluctuating hydrodynamics with the finite volume method. It provides fluid solvers for the compressible and incompressible Navier-Stokes equations using an Eulerian-Lagrangian approach. It offers 18 simulation schemes such as third order Runge-Kutta (RK3), thermo-statistics, and particle-wall. In this work the default RK3 scheme, which consists of kernel RK3\_1 and RK3\_2, is being evaluated.

SCALE-LES is a large-eddy simulation model developed for weather and climate study. Wahib and Maruyama[12] manually implemented the model using CUDA Fortran and OpenACC. The stencil kernels we evaluated (i.e. Scale\_1 and Scale\_1) are two of the most time-consuming ones.

McLachlan code [13] is a part of Einstein Toolkit, and BSSN formulations are a set of coupled nonlinear partial differential equations with 25 GFs. We study *Advect* and *Dalpha\_1* out of BSSN's 11 calculations because of their representative stencil patterns and high data reuse.

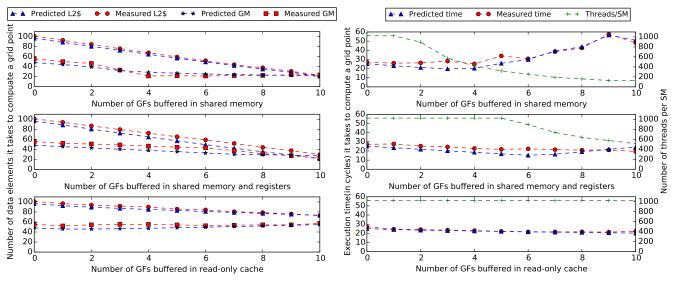

(a) Data transaction at L2 cache and global memory

(b) Execution time and thread-level parallelism

Figure 1: Evaluating performance model using a micro-benchmark.

# VIII. RESULTS

We first demonstrate the accuracy of the proposed performance model, we then demonstrate the effectiveness of the efficiency-based algorithm running stencil applications.

# A. Validation of the Performance Model

Figure 1a shows data transaction at L2 cache and global memory with different number of GFs being buffered and in three different ways. It can be seen that the predicted and measured number of data transactions is close for all buffering methods, though the predicted values are slightly smaller in general. This discrepancy is probably because our model assume GPU hardware and the compiler can avoid unnecessary data transaction in a very efficient way. Another interesting observation is that the L2 cache efficiently reduces the number of data transactions reaching global memory.

Figure 1b shows a comparison between the predicted and measured execution time, and the corresponding thread-level parallelism. Execution time is shown in cycle per grid point per SM. We can see that the predicted execution time and the measured ones match well except when thread-level parallelism changes. Take buffering strategy using shared memory for example, noticeable gap exists for 2, 3, 4, and 5 GFs being buffered. This is because as thread-level parallelism decreases, operation latency (including arithmetic and memory accesses) will be worse hidden. However, it is hard to accurately estimate the degree of latency hidden, compared with the data transaction.

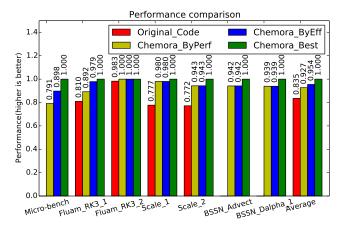

Figure 2: Normalized performance of different stencil.

# B. Effectiveness of the Efficiency-Based Scheme

The effectiveness of the efficiency-based assignment algorithm was evaluated by running a set of benchmarks on systems using the efficiency-based scheme, *Chemora\_ByEff*, and one that chooses based only on performance *Chemora\_ByPerf*. In addition, configurations were run in which assignment is based on a large search and manual tuning, *Chemora\_Best*, and hand-tuned versions of the code, *Original\_Code*. The run times are plotted in Figure 2, normalized to *Chemora\_Best*.

As we can see, Chemora\_ByEff is better than Chemora\_ByPerf on two runs, and equal on the others. Chemora\_ByEff has an edge where GFs' data access patterns within a kernel vary, where all GF have identical patterns the two schemes are equal.

For comparison, the performance of the original CUDA

code for *Fluam* [11] and *Scale-les* [12] running on the test system is shown. Chemora outperforms the original code for a number of reasons, such as dynamic compilation and efficient memory access and buffering code. These aspects of Chemora will be reported elsewhere.

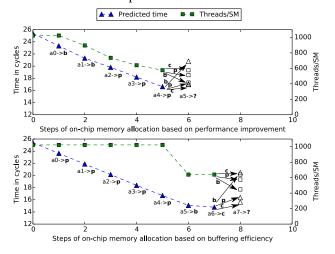

Figure 3: Case study of the efficiency-based scheme using micro-benchmark: ByPerf(top) vs ByEff(bottom).

Figure 3 shows a case study of the proposed efficiency-based assignment scheme. Initially, all GFs a0-a9 are unbuffered. At each step, a GF will be buffered in one of three ways, depends on their performance improvement or buffering efficiency. Scheme *ByPerf* buffers two GFs using shared memory in the first steps, results in fast drop of occupancy and no improvement to buffer the 6th GF. In contrast, scheme *ByEff* has 7 GFs being buffered at the end, resulting in minimum predicted execution time.

# IX. CONCLUSIONS

In this work, we first propose a performance model which supports five buffering strategies. Next, we present an efficiency-based assignment algorithm which can effectively reduce searching time from  $O(5^N)$  to  $O(N^2)$  where N denotes the number of GFs in a kernel. Experiments show good prediction accuracy. In addition, the performance achieved by the algorithm is 95.4%, on average, that of the manual tuned implementation. Future work could be evaluation: a) on other GPUs; b) with kernel fusion and fission.

#### X. ACKNOWLEDGMENTS

We thank Frank Löffler, Peter Diener, Roland Haas, Ian Hinder, and Jian Tao as the main authors of Chemora. Cactus and Chemora are currently supported by NSF awards 0905046 PetaCactus: Unraveling the supernova — Gammaray burst mystery; 0941653 Enabling Science at the Petascale: From Binary Systems and Stellar Core Collapse To Gamma-Ray Bursts; 1212401, 1212426, 1212433, 1212460 The Einstein Toolkit — An open source general relativistic multi-physics infrastructure for relativistic astrophysics;

1265449, 1265434, 1265451 Using PDE descriptions to generate code precisely tailored to energy-constrained systems including large GPU accelerated clusters. We would also like to thank NVIDIA Corporation for providing some of the GPUs used for this study.

Our research was made possible by access to HPC resources at Louisiana State University, in particular the Shelob cluster using the allocations hpc\_numrel and hpc\_hyrel.

#### REFERENCES

- [1] J. Meng and K. Skadron, "Performance modeling and automatic ghost zone optimization for iterative stencil loops on GPUs," in *Proceedings of the 23rd international conference on Supercomputing*, 2009, pp. 256–265.

- [2] Y. Zhang and F. Mueller, "Auto-generation and auto-tuning of 3D stencil codes on GPU clusters," in *Proceedings of the Tenth International Symposium on Code Generation and Optimization*, 2012, pp. 155–164.

- [3] S. Hong and H. Kim, "An analytical model for a GPU architecture with memory-level and thread-level parallelism awareness," in *Proceedings of the 36th Annual International Symposium on Computer Architecture*, 2009, pp. 152–163.

- [4] Y. Hu, D. M. Koppelman, S. R. Brandt, and F. Löffler, "Model-driven auto-tuning of stencil computations on GPUs," *HiStencils* 2015.

- [5] N. Maruyama and T. Aoki, "Optimizing stencil computations for NVIDIA Kepler GPUs," *HiStencils* 2014, p. 89, 2014.

- [6] Y. Yang, P. Xiang, M. Mantor, N. Rubin, and H. Zhou, "Shared memory multiplexing: a novel way to improve gpgpu throughput," in *Proceedings of the 21st international confer*ence on Parallel architectures and compilation techniques, 2012, pp. 283–292.

- [7] A. B. Hayes and E. Z. Zhang, "Unified on-chip memory allocation for SIMT architecture," in *Proceedings of the 28th ACM intl. conf. on Supercomputing*, 2014, pp. 293–302.

- [8] M. Gebhart, S. W. Keckler, B. Khailany, R. Krashinsky, and W. J. Dally, "Unifying primary cache, scratch, and register file memories in a throughput processor," in *Proceedings of* the 2012 45th Annual IEEE/ACM International Symposium on Microarchitecture, 2012, pp. 96–106.

- [9] "Chemora project website," http://chemoracode.org/index. php/Main\_Page.

- [10] NVIDIA Corporation, "NVIDIA's next generation cuda compute architecture: Kepler GK110," NVIDIA Corporation, Tech. Rep., 2013.

- [11] F. B. Usabiaga, "Minimal models for finite particles in fluctuating hydrodynamics," Ph.D. dissertation, Universidad Autónoma de Madrid, 2014.

- [12] M. Wahib and N. Maruyama, "Highly optimized full GPU-acceleration of non-hydrostatic weather model scale-les," in Cluster Computing (CLUSTER), 2013 IEEE International Conference on, 2013, pp. 1–8.

- [13] M. Blazewicz, I. Hinder, D. M. Koppelman, S. R. Brandt, M. Ciznicki, M. Kierzynka, F. Löffler, E. Schnetter, and J. Tao, "From physics model to results: An optimizing framework for cross-architecture code generation," *Scientific Programming*, vol. 21, no. 1, pp. 1–16, 2013.