## EE 4720

The SPARC assembly language program below is used in the problems that follow. SPARC register names are %g0-%g7, %i0-%i7, %l0-%l7, and %o0-%o7; and %g0 is a zero register (like r0 in DLX). The destination for arithmetic, logical, and load instructions is the rightmost register (add %l1,%l2,%l3 means %l3=%l1+%l2). SPARC uses a condition code register and special condition-code-setting instructions for branches. Branches include a delay slot.

```

LOOP:

```

```

ld [%11], %12

! Load 12 = MEM[ 11 ]

addcc %12, %g0, %g0

! g0 = g0 + 12. Sets cond. codes. Note: g0 is zero reg.

be DONE

! Branch if result zero.

! Fill delay slot with nop.

nop

add %16, %12, %16

! 16 = 16 + 12

! g0 = 1 & 13. Sets cond. codes. Note: g0 is zero reg.

andcc %13, 1, %g0

be SKIP1

nop

add %14, 1, %14

SKIP1:

subcc %13, 1000, %g0

! Branch if >= 0;

bpos SKIP2

nop

add %14, %13, %14

SKIP2:

andcc %13, 1, %g0

be SKIP3

nop

add %14, %14, %14

SKIP3:

add %11, 4, %11

ba LOOP

! Branch always. (Jump.)

nop

DONE:

```

**Problem 1:** An execution of the code above on a SPARC implementation takes 1000 cycles. The dynamic instruction count is  $IC_{all}$  of which  $IC_{nop}$  instructions are **nop**'s. Consider two ways of computing CPI:

$$CPI_A = \frac{t}{IC_{all}}$$

and  $CPI_B = \frac{t}{IC_{all} - IC_{nop}}$

where t is the execution time in cycles. Which is better? Justify your answer; an argument for either formula can be correct.

**Problem 2:** SPARC branches have a one-instruction delay slot, in the code above they are filled with nop's. Re-write the code filling as many slots with useful instructions as possible, reducing the number of instructions in the program.

**Problem 3**: Re-write the program in DLX, taking advantage of DLX's use of general purpose registers for specifying branch conditions.

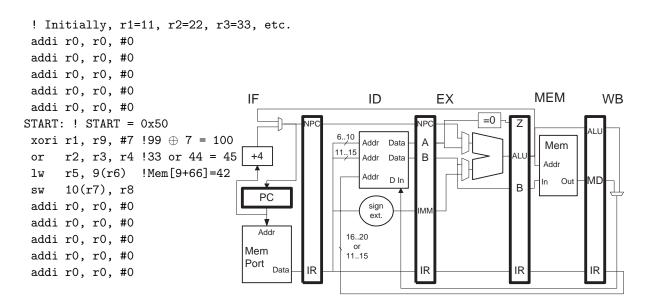

**Problem 4**: The program below executes on the DLX implementation shown below. The comments show the results of the xori, or, and lw instructions.

The table below shows the contents of pipeline registers and changes to architecturally visible registers r1-r31 over time. Cycle zero is the time that xori is in instruction fetch. The first two columns are completed, continue filling the table up until the sw instruction finishes writeback. Ignore values which are not used and which depend on the func field of type-R instructions. Values which are not used and don't depend on the func field should be shown. The output of the data memory is zero when a store or no memory operation is performed. The row labeled "Reg. Chng." shows a new register value that is available at the beginning of the cycle. If no register value is written leave the entry blank.

| Cycle      | 0                     | 1                     | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 |

|------------|-----------------------|-----------------------|---|---|---|---|---|---|---|---|----|

| PC         | 0×50                  | 0×54                  |   |   |   |   |   |   |   |   |    |

| IF/ID.IR   | əddi                  | xori                  |   |   |   |   |   |   |   |   |    |

| Reg. Chng. | $\texttt{r0} \gets 0$ | $\texttt{r0} \gets 0$ |   |   |   |   |   |   |   |   |    |

| ID/EX.IR   | əddi                  | addi                  |   |   |   |   |   |   |   |   |    |

| ID/EX.A    | 0                     | 0                     |   |   |   |   |   |   |   |   |    |

| ID/EX.B    | 0                     | 0                     |   |   |   |   |   |   |   |   |    |

| ID/EX.IMM  | 0                     | 0                     |   |   |   |   |   |   |   |   |    |

| EX/MEM.IR  | əddi                  | Iqqi                  |   |   |   |   |   |   |   |   |    |

| EX/MEM.ALU | 0                     | 0                     |   |   |   |   |   |   |   |   |    |

| EX/MEM.B   | 0                     | 0                     |   |   |   |   |   |   |   |   |    |

| MEM/WB.IR  | əddi                  | Iqqi                  |   |   |   |   |   |   |   |   |    |

| MEM/WB.ALU | 0                     | 0                     |   |   |   |   |   |   |   |   |    |

| MEM/WB.MD  | 0                     | 0                     |   |   |   |   |   |   |   |   |    |

| •I         |                       |                       |   |   | 2 |   |   |   |   |   |    |