## Verilog Scheduling and Event Queue

Consider

always\_ff @( posedge clk ) c = reset ? 0 : c + 1;

always\_ff @( posedge clk ) over\_th = c + 1'd1 > threshold;

Is over\_th computed using the new or old c?

(Answer: either one, and so code is unreliable.)

## Terminology

### Event:

Sort of a to-do item for simulator. May include running a bit of Verilog code or updating an object's value.

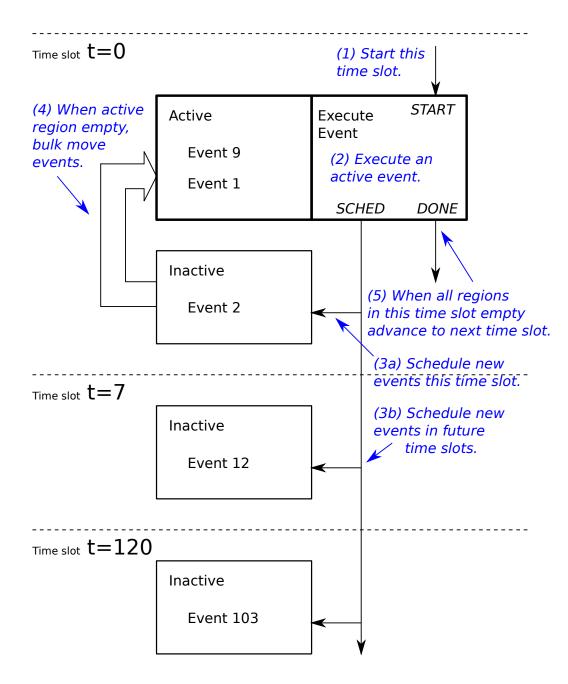

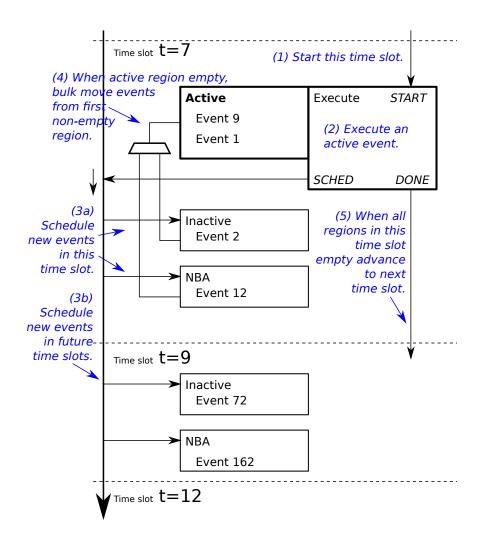

### Event Queue:

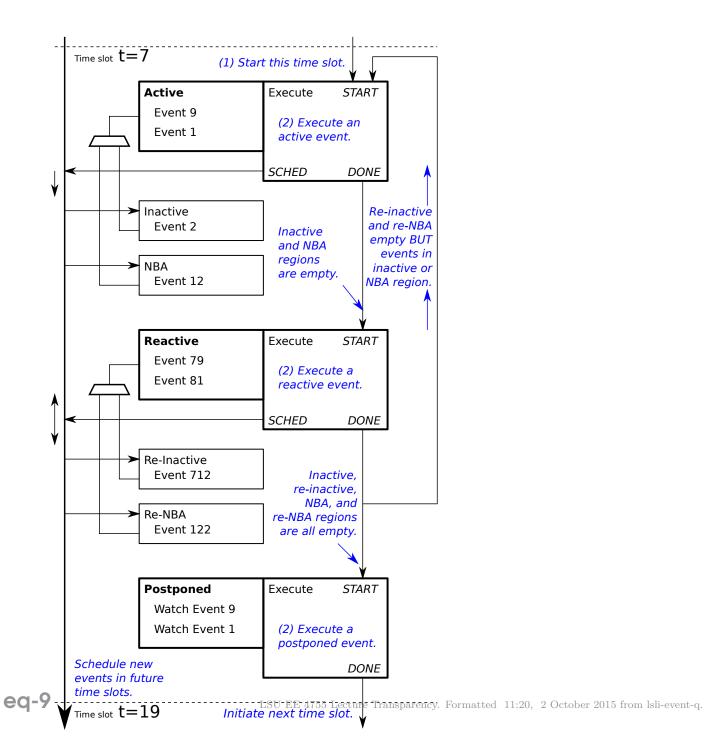

Sort of a to-do list for simulator. It is divided into time slots and time slot regions.

### Time Slot:

A section of the event queue in which all events have the same time stamp.

### Time Slot Region:

A subdivision of a time slot. There are many of these. Important ones: active, inactive, NBA.

### Scheduling:

Determining when an event should execute. The when consists of a time slot and a time slot region.

## Update Events:

The changing of an object's value. Will cause \*sensitive\* objects to be scheduled.

# Example

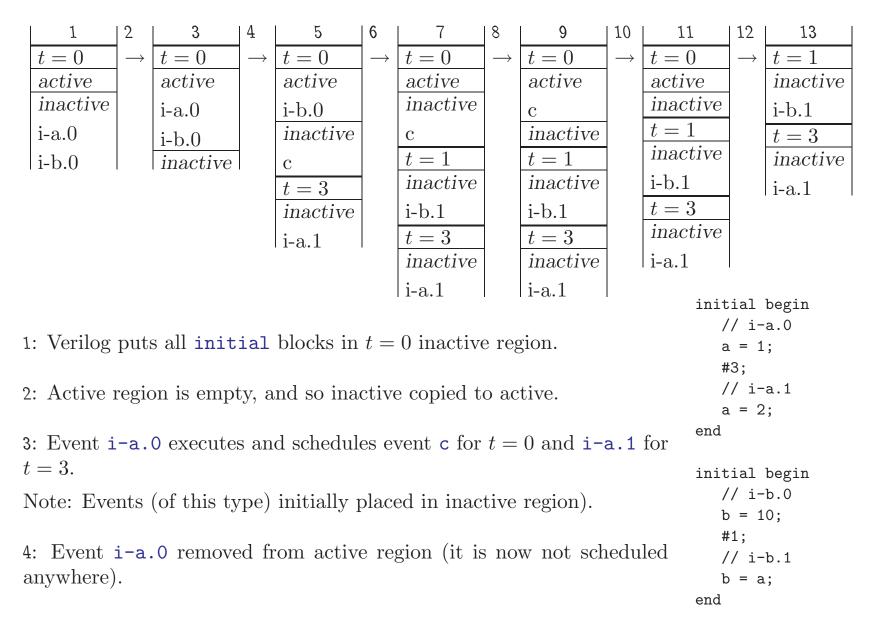

eq-4

5,6: Event i-b.0 executes and schedules i-b.1 for t = 1.

7,8: Since active region is empty, inactive region is bulk-copied to active region.

9: Event c executes.

10-12: Since all regions in time slot 0 are empty, move to next time slot, t = 1.

## Event Scheduling

#### Time-Delay Scheduled

Scheduled by a delay: #4 a = b;

#### Sensitivity List Scheduled

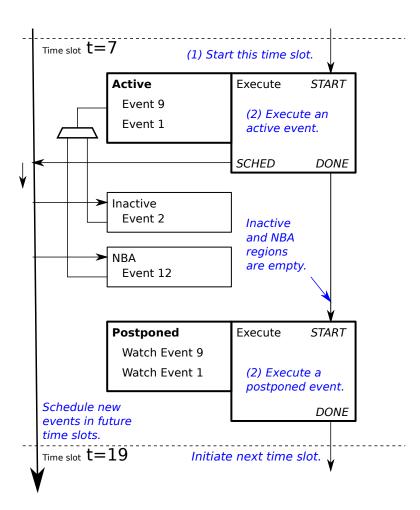

Explicit event @( a ), @( posedge clk), wait( stop\_raining )

Continuous assignment: assign x = a + b;.

Module or primitive ports: and myAndGate(x,a,b) .

#### Permanently Scheduled

Watch lists: \$watch(a).

# Schedule [verb]

Event

Evaluation Event

Update Event

## Time

Time Slot