////////////////////////////////////////////////////////////////////////////////

///

/// Solution to LSU EE 3755 Fall 2001 Homework 2

///

////////////////////////////////////////////////////////////////////////////////

/// Problem 1 Solution

///

module uni_striped_c(us,v);

input [31:0] v;

output us;

reg us;

integer i;

reg [4:0] width, this;

reg last;

reg [1:0] state;

parameter st_in_first_stripe = 0;

parameter st_okay_so_far = 1;

parameter st_not_uniform = 2;

always @( v )

begin

state = st_in_first_stripe;

width = 0;

this = 0;

last = 1;

for(i=0; i<32; i=i+1)

begin

if( state == st_in_first_stripe )

begin

if( v[i] == last )

begin

width = width + 1;

end

else

begin

state = i ? st_okay_so_far : st_not_uniform;

this = width - 1;

end

end

else

begin

if( v[i] == last )

begin

this = this - 1;

end

else

begin

if( this ) state = st_not_uniform;

this = width - 1;

end

end

last = v[i];

end

us = state == st_okay_so_far ? 1 : 0;

end

endmodule

////////////////////////////////////////////////////////////////////////////////

/// Problem 2 Solution

///

module uni_striped_s(us,bit,clk,start);

input bit, clk, start;

output us;

reg us;

reg [5:0] width, this;

reg last;

reg [1:0] state;

parameter st_in_first_stripe = 0;

parameter st_okay_so_far = 1;

parameter st_not_uniform = 2;

always @( posedge clk )

begin

if( start )

begin

state = st_in_first_stripe;

width = 0;

this = 0;

last = 1;

us = 0;

end

if( state == st_in_first_stripe )

begin

if( bit == last )

begin

width = width + 1;

end

else

begin

state = start ? st_not_uniform : st_okay_so_far;

this = width - 1;

end

end

else

begin

if( bit == last )

begin

if( !this ) state = st_not_uniform;

this = this - 1;

end

else

begin

if( this ) state = st_not_uniform;

this = width - 1;

end

end

us = state == st_not_uniform ? 0 : 1;

last = bit;

end

endmodule

////////////////////////////////////////////////////////////////////////////////

/// Problem 3

///

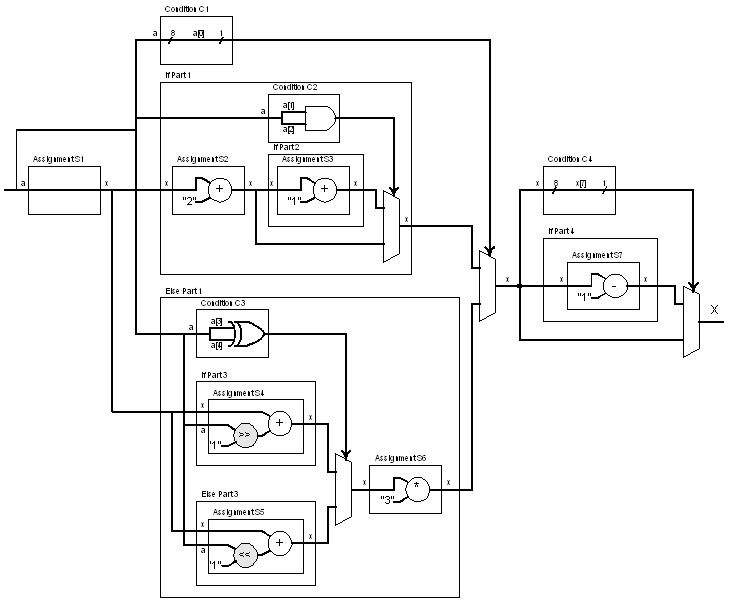

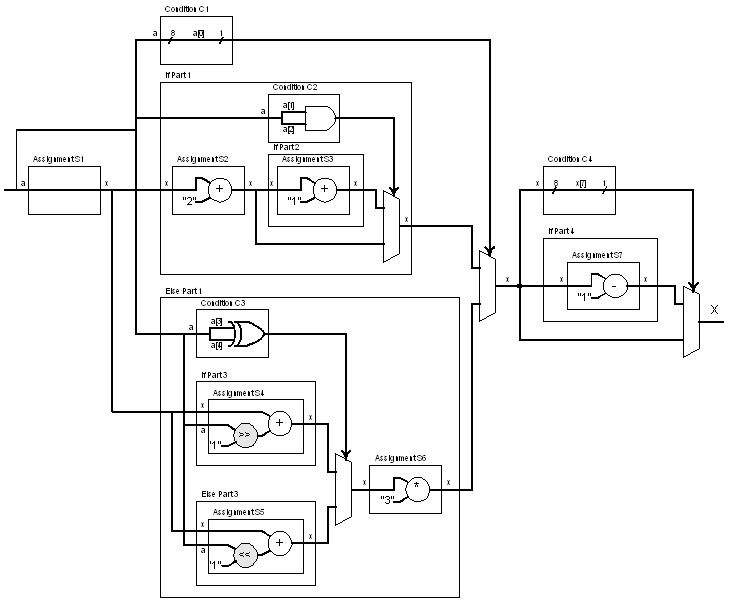

// Labels (in comments) have been added to the module identifying

// assignments, ifpart, etc. These labels appear in the image below.

// Note: The left- and right-shift components are not actual hardware,

// just a renumbering of bit positions and insertion of a zero.

// Solution

// Also available in PDF: http://www.ece.lsu.edu/ee3755/2001f/hw2solp3.pdf

module andyetanotherif(x,a);

input [7:0] a;

output x;

reg [7:0] x;

always @( a )

begin

x = a; // Assignment S1

if( a[0] ) // If 1, Condition C1

begin // If Part 1

x = x + 2; // Assignment S2

if( a[1] & a[2] ) // If 2, Condition C2

// If Part 2

x = x + 1; // Assignment S3

end

else

begin // Else Part 1 (part of If 1)

if( a[3] ^ a[4] ) // If 3, Condition C3

// If Part 3

x = x + ( a >> 1 ); // Assignment S4

else

// Else Part 3

x = x + ( a << 1 ); // Assignment S5

x = 3 * x; // Assignment S6

end // End of Else Part 1

if( x[7] ) // If 4, Condition C4

// If Part 4

x = x - 1; // Assignment S7

end

endmodule

// Also available in PDF: http://www.ece.lsu.edu/ee3755/2001f/hw2solp3.pdf

module andyetanotherif(x,a);

input [7:0] a;

output x;

reg [7:0] x;

always @( a )

begin

x = a; // Assignment S1

if( a[0] ) // If 1, Condition C1

begin // If Part 1

x = x + 2; // Assignment S2

if( a[1] & a[2] ) // If 2, Condition C2

// If Part 2

x = x + 1; // Assignment S3

end

else

begin // Else Part 1 (part of If 1)

if( a[3] ^ a[4] ) // If 3, Condition C3

// If Part 3

x = x + ( a >> 1 ); // Assignment S4

else

// Else Part 3

x = x + ( a << 1 ); // Assignment S5

x = 3 * x; // Assignment S6

end // End of Else Part 1

if( x[7] ) // If 4, Condition C4

// If Part 4

x = x - 1; // Assignment S7

end

endmodule

// Also available in PDF: http://www.ece.lsu.edu/ee3755/2001f/hw2solp3.pdf

module andyetanotherif(x,a);

input [7:0] a;

output x;

reg [7:0] x;

always @( a )

begin

x = a; // Assignment S1

if( a[0] ) // If 1, Condition C1

begin // If Part 1

x = x + 2; // Assignment S2

if( a[1] & a[2] ) // If 2, Condition C2

// If Part 2

x = x + 1; // Assignment S3

end

else

begin // Else Part 1 (part of If 1)

if( a[3] ^ a[4] ) // If 3, Condition C3

// If Part 3

x = x + ( a >> 1 ); // Assignment S4

else

// Else Part 3

x = x + ( a << 1 ); // Assignment S5

x = 3 * x; // Assignment S6

end // End of Else Part 1

if( x[7] ) // If 4, Condition C4

// If Part 4

x = x - 1; // Assignment S7

end

endmodule

// Also available in PDF: http://www.ece.lsu.edu/ee3755/2001f/hw2solp3.pdf

module andyetanotherif(x,a);

input [7:0] a;

output x;

reg [7:0] x;

always @( a )

begin

x = a; // Assignment S1

if( a[0] ) // If 1, Condition C1

begin // If Part 1

x = x + 2; // Assignment S2

if( a[1] & a[2] ) // If 2, Condition C2

// If Part 2

x = x + 1; // Assignment S3

end

else

begin // Else Part 1 (part of If 1)

if( a[3] ^ a[4] ) // If 3, Condition C3

// If Part 3

x = x + ( a >> 1 ); // Assignment S4

else

// Else Part 3

x = x + ( a << 1 ); // Assignment S5

x = 3 * x; // Assignment S6

end // End of Else Part 1

if( x[7] ) // If 4, Condition C4

// If Part 4

x = x - 1; // Assignment S7

end

endmodule